# JVC SERVICE MANUAL

# CD RECEIVER

# KD-S747

# TABLE OF CONTENTS

| 1 | Important Safety Precautions | 1-2  |

|---|------------------------------|------|

| 2 | Disassembly method           | 1-4  |

| 3 | Adjustment                   | 1-23 |

| 4 | Description of major ICs 1   | 1-27 |

## SECTION 1 Important Safety Precautions

#### 1.1 Safety Precautions

A CAUTION Burrs formed during molding may be left over on some parts of the chassis. Therefore, pay attention to such burrs in the case of preforming repair of this system.

A CAUTION Please use enough caution not to see the beam directly or touch it in case of an adjustment or operation check.

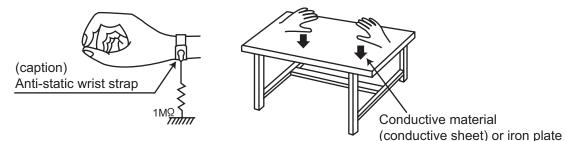

#### 1.2 Preventing static electricity

Electrostatic discharge (ESD), which occurs when static electricity stored in the body, fabric, etc. is discharged, can destroy the laser diode in the traverse unit (optical pickup). Take care to prevent this when performing repairs.

#### 1.2.1 Grounding to prevent damage by static electricity

Static electricity in the work area can destroy the optical pickup (laser diode) in devices such as DVD players. Be careful to use proper grounding in the area where repairs are being performed.

(1) Ground the workbench

Ground the workbench by laying conductive material (such as a conductive sheet) or an iron plate over it before placing the traverse unit (optical pickup) on it.

(2) Ground yourself

Use an anti-static wrist strap to release any static electricity built up in your body.

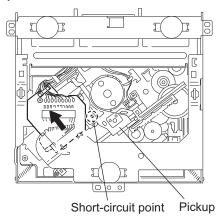

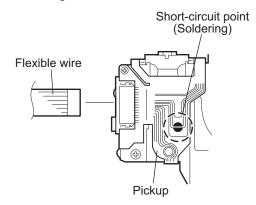

(3) Handling the optical pickup

- In order to maintain quality during transport and before installation, both sides of the laser diode on the replacement optical pickup are shorted. After replacement, return the shorted parts to their original condition. (Refer to the text.)

- Do not use a tester to check the condition of the laser diode in the optical pickup. The tester's internal power source can easily destroy the laser diode.

#### 1.3 Handling the traverse unit (optical pickup)

- (1) Do not subject the traverse unit (optical pickup) to strong shocks, as it is a sensitive, complex unit.

- (2) Cut off the shorted part of the flexible cable using nippers, etc. after replacing the optical pickup. For specific details, refer to the replacement procedure in the text. Remove the anti-static pin when replacing the traverse unit. Be careful not to take too long a time when attaching it to the connector.

- (3) Handle the flexible cable carefully as it may break when subjected to strong force.

- (4) It is not possible to adjust the semi-fixed resistor that adjusts the laser power. Do not turn it.

#### 1.4 Attention when traverse unit is decomposed

#### \*Please refer to "Disassembly method" in the text for the CD pickup unit.

- Apply solder to the short land before the flexible wire is disconnected from the connector on the CD pickup unit. (If the flexible wire is disconnected without applying solder, the CDpickup may be destroyed by static electricity.)

- In the assembly, be sure to remove solder from the short land after connecting the flexible wire.

# SECTION 2 Disassembly method

#### 2.1 Main body

# 2.1.1 Removing the front panel assembly (See Fig.1)

(1) Push the detach button in the lower right part of the front panel assembly and remove the front panel assembly in the direction of the arrow.

# Front panel assembly

Fig.1

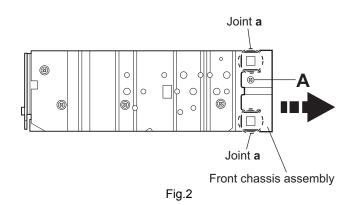

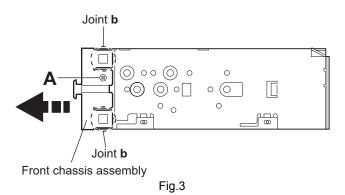

# 2.1.2 Removing the front chassis assembly (See Figs.2 and 3)

- Prior to performing the following procedure, remove the front panel assembly.

- (1) Remove the screw **A** on the both sides of the main body.

- (2) Release the two joints **a** and two joints **b** on both sides of the main body using a screwdriver, and remove the front chassis assembly forward.

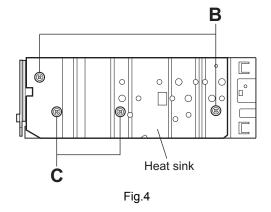

# 2.1.3 Removing the heat sink (See Fig.4)

(1) Remove the two screws **B** and two screws **C** on the left side of the main body.

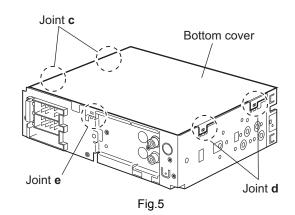

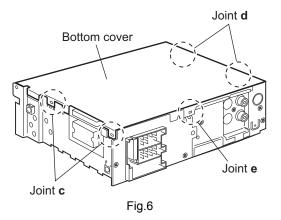

# 2.1.4 Removing the bottom cover (See Figs.5 and 6)

- Prior to performing the following procedure, remove the front panel assembly, front chassis assembly and heat sink.

- (1) Turn over the body and release the two joints c, two joints d and joint e.

#### CAUTION:

Do not damage the main board when releasing the joint  $\, e \,$  using a screwdriver. (See Figs.5 and 6)

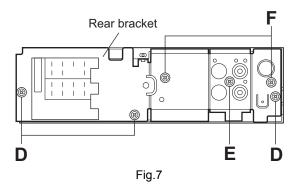

#### 2.1.5 Removing the rear bracket (See Fig.7)

- · Prior to performing the following procedure, remove the front panel assembly, front chassis assembly, heat sink and bottom cover.

- (1) Remove the three screws  ${\bf D},$  screw  ${\bf E}\,$  and two screws  ${\bf F}\,$  on the back of the body.

- (2) Remove the rear bracket.

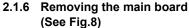

- · Prior to performing the following procedure, remove the front panel assembly, front chassis assembly, heat sink, bottom cover and rear bracket.

- (1) Remove the two screws **G** attaching the main board.

- (2) Disconnect connector CN501 and remove the main board.

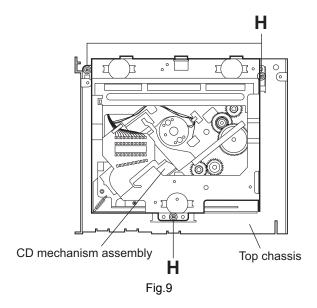

#### 2.1.7 Removing the CD mechanism assembly (See Fig.9)

- · Prior to performing the following procedure, remove the front panel assembly, front chassis assembly, heat sink, bottom cover, rear bracket and main board.

- (1) Remove the three screws  $\mathbf{H}$ .

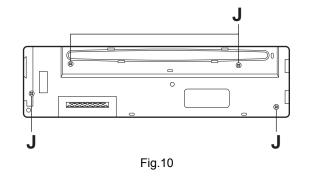

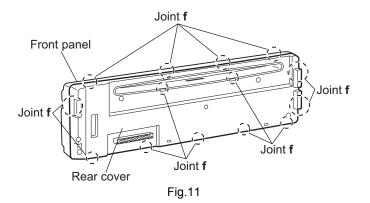

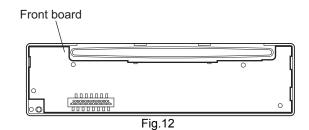

#### 2.1.8 Removing the front board (See Figs.10 to 12)

- · Prior to performing the following procedure, remove the front panel assembly.

- (1) Remove the four screws  $\mathbf{J}$  on the back side of the front panel assembly.

- (2) Release the twelve joints **f**.(3) Take out the front board.

#### 2.2 CD Mechanism Assembly

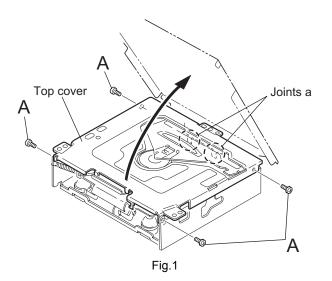

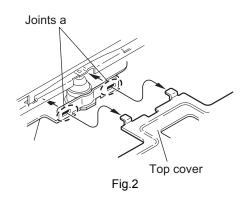

#### 2.2.1 Removing the top cover (See Figs.1 and 2)

- (1) Remove the two screws **A** on the both side of the body.

- (2) Lift the front side of the top cover and move the top cover backward to release the two joints **a**.

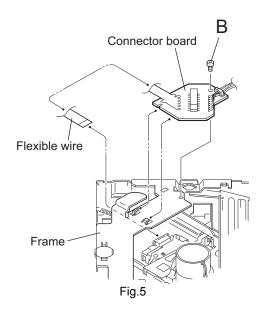

# 2.2.2 Removing the connector board (See Figs.3 to 5)

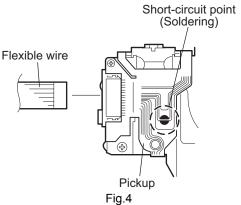

#### CAUTION:

Before disconnecting the flexible wire from the pickup, solder the short-circuit point on the pickup. No observance of this instruction may cause damage of the pickup.

- (1) Remove the screw  ${\bf B}$  fixing the connector board.

- (2) Solder the short-circuit point on the connector board.

- $(3) \ Disconnect the flexible wire from the pickup.$

- (4) Move the connector board in the direction of the arrow to release the two joints **b**.

- (5) Unsolder the wire on the connector board if necessary.

#### CAUTION:

Unsolder the short-circuit point after reassembling.

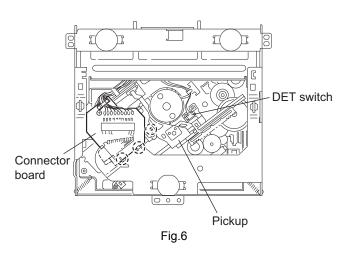

#### 2.2.3 Removing the DET switch

(See Figs.6 and 7)

- (1) Extend the two tabs **c** of the feed sw. holder and pull out the switch.

- (2) Unsolder the DET switch wire if necessary.

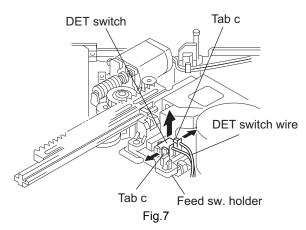

# 2.2.4 Removing the chassis unit (See Figs.8 and 9)

- Prior to performing the following procedure, remove the top cover and connector board.

- (1) Remove the two suspension springs (L) and (R) attaching the chassis unit to the frame.

#### CAUTION:

- The shape of the suspension spring (L) and (R) are different. Handle them with care.

- When reassembling, make sure that the three shafts on the underside of the chassis unit are inserted to the dampers certainly.

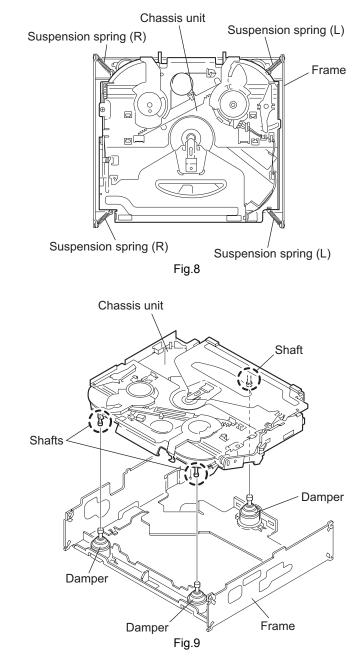

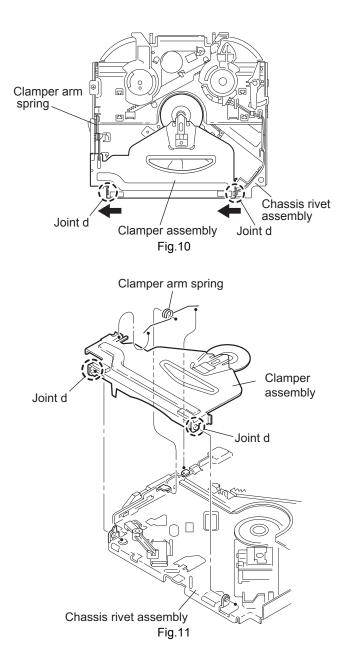

- 2.2.5 Removing the clamper assembly (See Figs.10 and 11)

- Prior to performing the following procedure, remove the top cover.

- (1) Remove the clamper arm spring.

- (2) Move the clamper assembly in the direction of the arrow to release the two joints **d**.

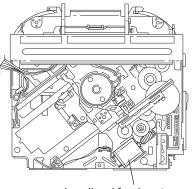

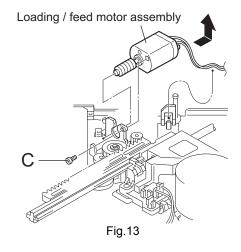

# 2.2.6 Removing the loading / feed motor assembly (See Figs.12 and 13)

- Prior to performing the following procedure, remove the top cover, connector board and chassis unit.

- (1) Remove the screw **C** and move the loading / feed motor assembly in the direction of the arrow to remove it from the chassis rivet assembly.

- (2) Disconnect the wire from the loading / feed motor assembly if necessary.

#### CAUTION:

When reassembling, connect the wire from the loading / feed motor assembly to the flame as shown in Fig.12.

Loading / feed motor assembly Fig.12

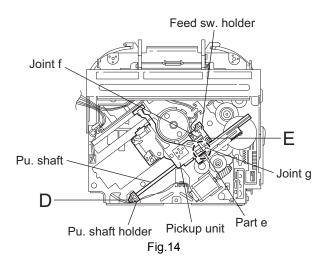

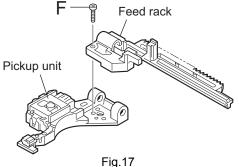

# 2.2.7 Removing the pickup unit (See Figs.14 to 18)

- Prior to performing the following procedure, remove the top cover, connector board and chassis unit.

- (1) Remove the screw **D** and pull out the pu. shaft holder from the pu. shaft.

- (2) Remove the screw E attaching the feed sw. holder.

- (3) Move the part e of the pickup unit upward with the pu. shaft and the feed sw. holder, then release the joint f of the feed sw. holder in the direction of the arrow. The joint g of the pickup unit and the feed rack is released, and the feed sw. holder comes off.

- (4) Remove the pu. shaft from the pickup unit.

- (5) Remove the screw **F** attaching the feed rack to the pickup unit.

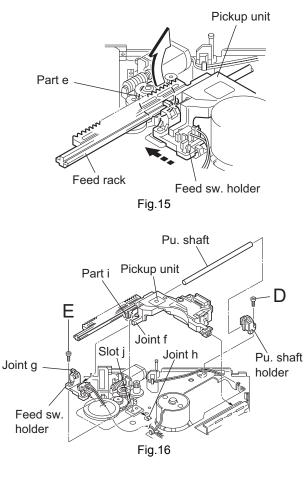

# 2.2.8 Reattaching the pickup unit (See Figs.14 to 17)

- (1) Reattach the feed rack to the pickup unit using the screw F.

- (2) Reattach the feed sw. holder to the feed rack while setting the joint g to the slot of the feed rack and setting the part f of the feed rack to the switch of the feed sw. holder correctly.

- (3) As the feed sw. holder is temporarily attached to the pickup unit, set to the gear of the joint g and to the bending part of the chassis (joint h) at a time.

#### CAUTION:

Make sure that the part i on the underside of the feed rack is certainly inserted to the slot j of the change lock lever.

- (4) Reattach the feed sw. holder using the screw E.

- (5) Reattach the pu. shaft to the pickup unit. Reattach the pu. shaft holder to the pu. shaft using the screw D.

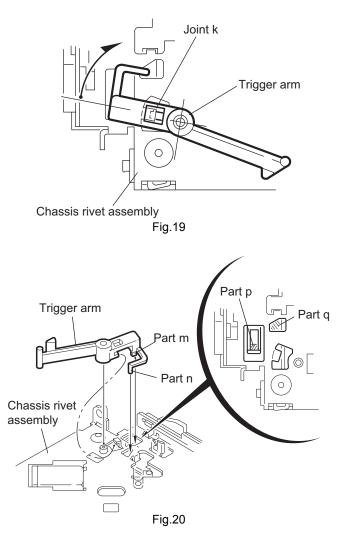

# 2.2.9 Removing the trigger arm (See Figs.19 and 20)

- Prior to performing the following procedure, remove the top cover, connector board and clamper unit.

- (1) Turn the trigger arm in the direction of the arrow to release the joint k and pull out upward.

#### CAUTION:

When reassembling, insert the part m and n of the trigger arm into the part p and q at the slot of the chassis rivet assembly respectively and join the joint k at a time.

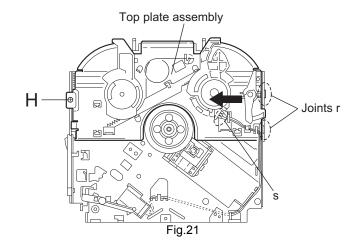

# 2.2.10 Removing the top plate assembly (See Fig.21)

- Prior to performing the following procedure, remove the top cover, connector board, chassis unit, and clamper assembly.

(1) Remove the screw H.

- (2) Move the top plate assembly in the direction of the arrow to release the two joints r.

- (3) Unsolder the wire marked s if necessary.

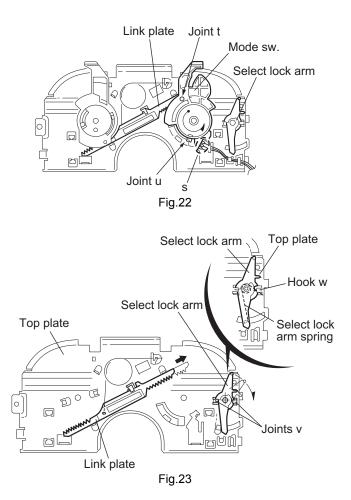

- 2.2.11 Removing the mode sw. / select lock arm (See Figs.22 and 23)

- Prior to performing the following procedure, remove the top plate assembly.

- (1) Bring up the mode sw. to release from the link plate (joint t) and turn in the direction of the arrow to release the joint u.

- (2) Unsolder the wire of the mode sw. marked s if necessary.

- (3) Turn the select lock arm in the direction of the arrow to release the two joints  ${\bf v}.$

- (4) The select lock arm spring comes off the select lock arm at the same time.

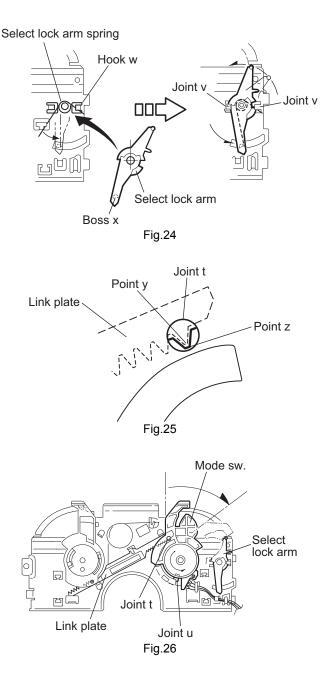

2.2.12 Reassembling the mode sw. / select lock arm (See Figs.24 to 26)

#### **REFERENCE:**

Reverse the above removing procedure.

- (1) Reattach the select lock arm spring to the top plate and set the shorter end of the select lock arm spring to the hook w on the top plate.

- (2) Set the other longer end of the select lock arm spring to the boss x on the underside of the select lock arm, and join the select lock arm to the slots (joint  $\mathbf{v}$ ). Turn the select lock arm as shown in the figure.

- (3) Reattach the mode sw. while setting the part t to the first peak of the link plate gear, and join the joint **u**.

#### CAUTION:

When reattaching the mode sw., check if the points y and z are correctly fitted and if each part operates properly.

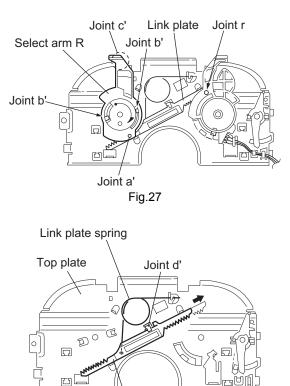

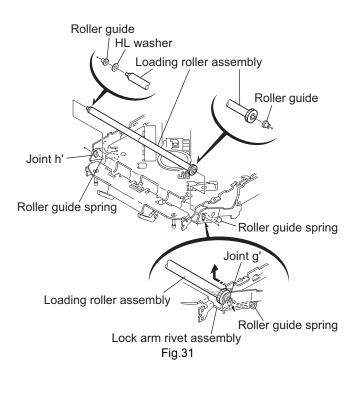

- 2.2.13 Removing the select arm R / link plate (See Figs.27 and 28)

- Prior to performing the following procedure, remove the top plate assembly.

- (1) Bring up the select arm R to release from the link plate (joint a') and turn as shown in the figure to release the two joints b' and joint c'.

- (2) Move the link plate in the direction of the arrow to release the joint d'. Remove the link plate spring at the same time.

#### REFERENCE:

Before removing the link plate, remove the mode sw..

#### 2.2.14 Reattaching the Select arm R / link plate (See Figs.29 and 30)

#### **REFERENCE:**

- Reverse the above removing procedure.

- (1) Reattach the link plate spring.

- (2) Reattach the link plate to the link plate spring while joining them at joint **d'**.

- (3) Reattach the joint a' of the select arm R to the first peak of the link plate while joining the two joints b' with the slots. Then turn the select arm R as shown in the figure. The top plate is joined to the joint c'.

#### CAUTION:

When reattaching the select arm R, check if the points **e'** and **f'** are correctly fitted and if each part operates properly.

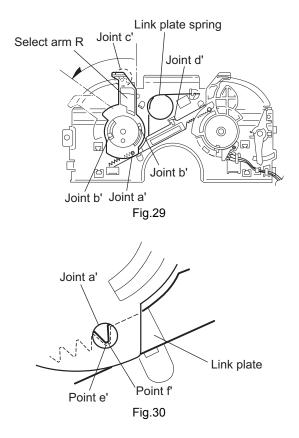

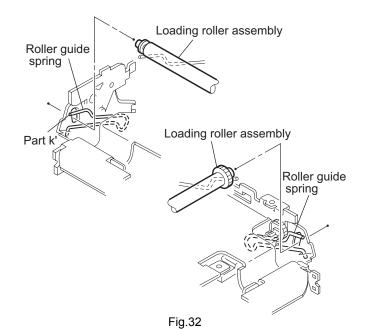

#### 2.2.15 Removing the loading roller assembly (See Figs.31 to 33)

- Prior to performing the following procedure, remove the clamper assembly and top plate assembly.

- (1) Push inward the loading roller assembly on the gear side and detach it upward from the slot of the joint **g'** of the lock arm rivet assembly.

- (2) Detach the loading roller assembly from the slot of the joint h' of the lock arm rivet assembly.

The roller guide comes off the gear section of the loading roller assembly.

Remove the roller guide and the HL washer from the shaft of the loading roller assembly.

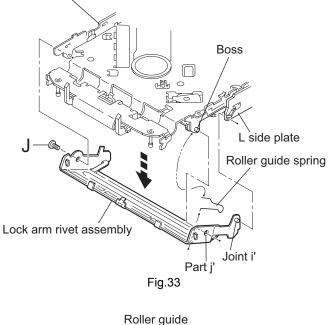

- (3) Remove the screw J attaching the lock arm rivet assembly.

- (4) Push the shaft at the joint i' of the lock arm rivet assembly inward to release the lock arm rivet assembly from the slot of the L side plate.

- (5) Extend the lock arm rivet assembly outward and release the joint j' from the boss of the chassis rivet assembly. The roller guide springs on both sides come off at the same time.

#### CAUTION:

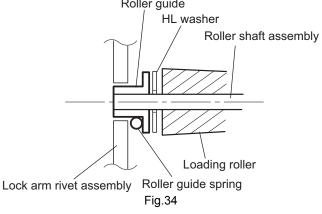

When reassembling, reattach the left and right roller guide springs to the lock arm rivet assembly before reattaching the lock arm rivet assembly to the chassis rivet assembly. Make sure to fit the part k' of the roller guide spring inside of the roller guide. (Refer to Fig.34.)

Chassis rivet assembly

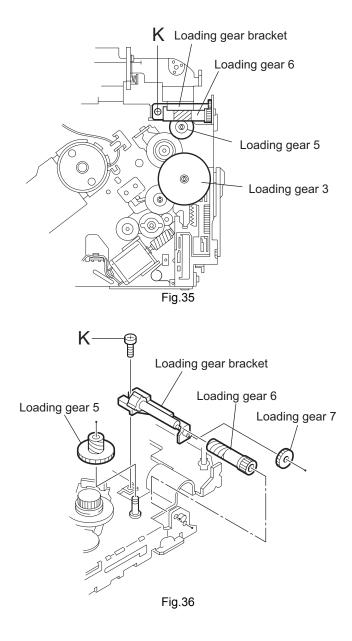

- 2.2.16 Removing the loading gear 5, 6 and 7 (See Figs.35 and 36)

- Prior to performing the following procedure, remove the top cover, chassis unit, pickup unit and top plate assembly.

- (1) Remove the screw K attaching the loading gear bracket. The loading gear 6 and 7 come off the loading gear bracket.

- (2) Pull out the loading gear 5.

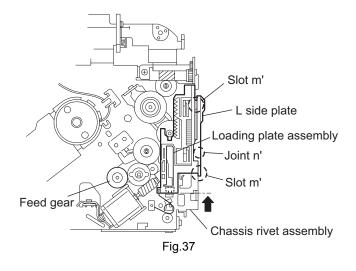

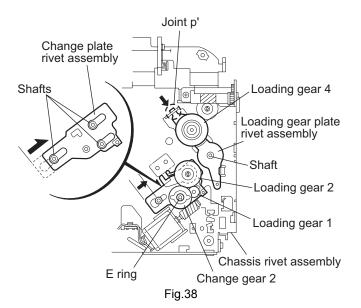

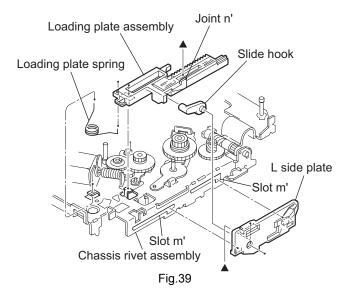

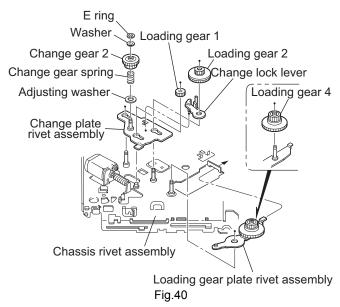

#### 2.2.17 Removing the gears (See Figs.37 to 40)

- Prior to performing the following procedure, remove the top cover, chassis unit, top plate assembly and pickup unit.

- Pull out the loading gear 3. (See Fig.35.)

- (1) Pull out the feed gear.

- (2) Move the loading plate assembly in the direction of the arrow to release the L side plate from the two slots m' of the chassis rivet assembly. (See Fig.37.)

- (3) Detach the loading plate assembly upward from the chassis rivet assembly while releasing the joint **n'**. Remove the slide hook and loading plate spring from the loading plate assembly.

- (4) Pull out the loading gear 2 and remove the change lock lever.

- (5) Remove the E ring and washer attaching the changer gear 2.

- (6) The changer gear 2, change gear spring and adjusting washer come off.

- (7) Remove the loading gear 1.

- (8) Move the change plate rivet assembly in the direction of the arrow to release from the three shafts of the chassis rivet assembly upward. (See Fig.38.)

- (9) Detach the loading gear plate rivet assembly from the shaft of the chassis rivet assembly upward while releasing the joint p'. (See Figs.38 and 40.)

- (10) Pull out the loading gear 4.

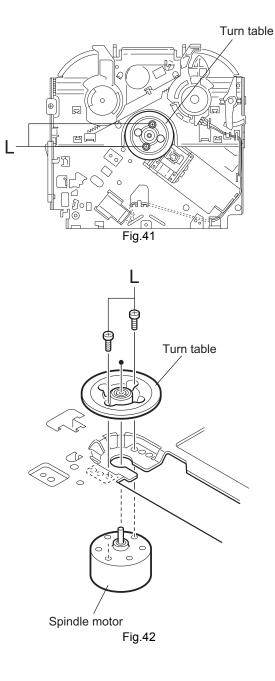

#### 2.2.18 Removing the turn table / spindle motor (See Figs.41 and 42)

- Prior to performing the following procedure, remove the top cover, connector board, chassis unit and clamper assembly.

(1) Remove the two screws L attaching the spindle motor assembly through the slot of the turn table on top of the body.

- (2) Unsolder the wire on the connector board if necessary.

## **SECTION 3** Adjustment

#### 3.1 Adjustment method

- Test instruments required for adjustment

- 1. Digital oscilloscope (100MHz)

- 2. AM Standard signal generator

- 3. FM Standard signal generator

- 4. Stereo modulator

- 5. Electric voltmeter

- 6. Digital tester

- 7. Tracking offset meter

- 8. Test Disc JVC :CTS-1000

- 9. Extension cable for check

- EXTSH002-22PX 1

- Standard volume position Balance and Bass & Treble volume : Indication"0" Loudness : OFF

- Frequency Band FM1/FM2 87.5MHz ~ 108.0MHz 65.0MHz ~ 74.0MHz FM3 MW 522kHz ~ 1620kHz LW 144kHz ~ 279kHz

- Dummy load

Exclusive dummy load should be used for AM, and FM. For FM dummy load, there is a loss of 6dB between SSG output and antenna input. The loss of 6dB need not be considered since direct reading of figures are applied in this working standard.

Standard measuring conditions Power supply voltage DC14.4V(11~16V) Load impedance 20Kohm(2 Speakers connection) Line out 2.0V (Vol. MAX) **Output Level**

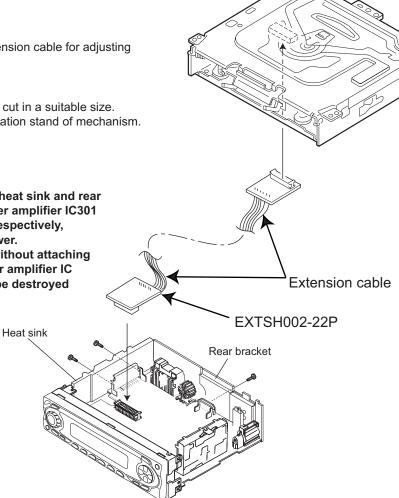

How to connect the extension cable for adjusting

\* The cardboard is cut in a suitable size. uses for the insulation stand of mechanism.

#### Caution:

Be sure to attach the heat sink and rear bracket onto the power amplifier IC301 and regulator IC901 respectively, before supply the power. If voltage is applied without attaching these parts, the power amplifier IC and regulator IC will be destroyed by heat.

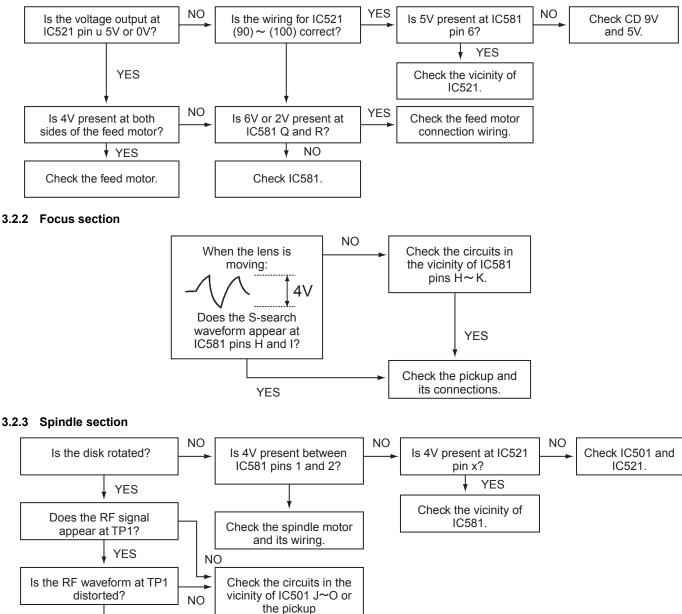

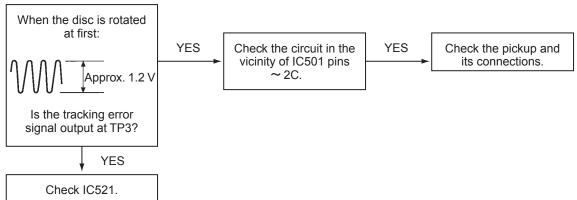

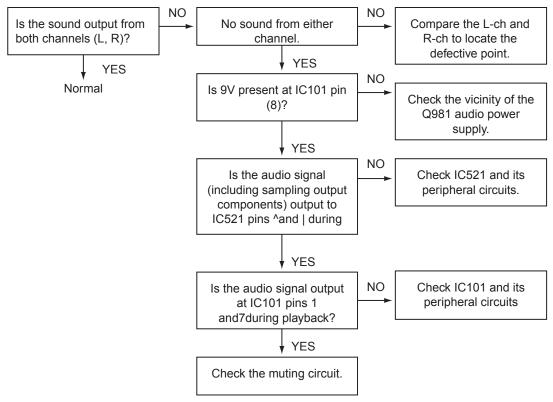

#### 3.2 Troubleshooting

#### 3.2.1 Feed section

section

Proceed to the Tracking

YES

#### 3.2.4 Tracking section

#### 3.2.5 Signal processing section

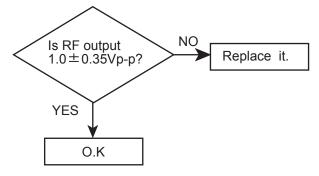

#### 3.3 Maintenance of laser pickup

(1) Cleaning the pick up lens

Before you replace the pick up, please try to clean the lens with a alcohol soaked cotton swab.

- (2) Life of the laser diode

- When the life of the laser diode has expired, the following symptoms will appear.

- The level of RF output (EFM output:ampli tude of eye pattern) will be low.

(3) Semi-fixed resistor on the APC PC board

The semi-fixed resistor on the APC printed circuit board which is attached to the pickup is used to adjust the laser power.Since this adjustment should be performed to match the characteristics of the whole optical block, do not touch the semi-fixed resistor.

If the laser power is lower than the specified value, the laser diode is almost worn out, and the laser pickup should be replaced.

If the semi-fixed resistor is adjusted while the pickup is functioning normally, the laser pickup may be damaged due to excessive current.

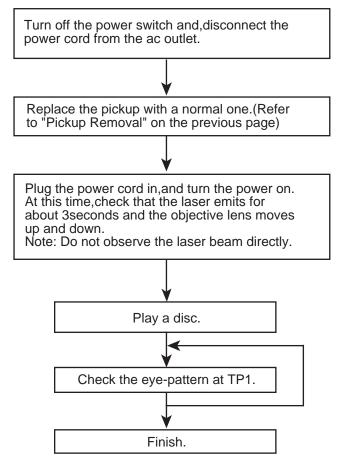

#### 3.4 Replacement of laser pickup

## SECTION 4 Description of major ICs

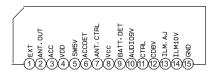

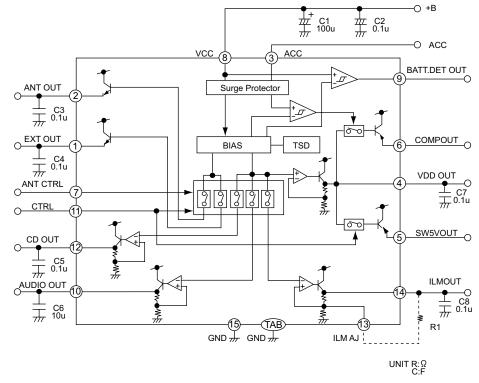

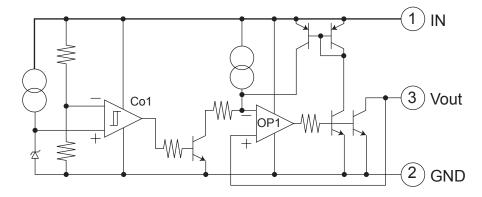

#### 4.1 HA13164A (IC901) : Regulator

• Terminal layout

· Block diagram

note1) TAB (header of IC) connected to GND

#### • Pin function

| Pin No. | Symbol                                                                                  | Function                                                     |  |  |  |  |  |

|---------|-----------------------------------------------------------------------------------------|--------------------------------------------------------------|--|--|--|--|--|

| 1       | 1 EXTOUT Output voltage is VCC-1 V when M or H level applied to CTRL pin.               |                                                              |  |  |  |  |  |

| 2       | ANTOUT Output voltage is VCC-1 V when M or H level to CTRL pin and H level to ANT-CTRL. |                                                              |  |  |  |  |  |

| 3       | ACCIN                                                                                   | Connected to ACC.                                            |  |  |  |  |  |

| 4       | VDDOUT                                                                                  | Regular 5.7V.                                                |  |  |  |  |  |

| 5       | SW5VOUT                                                                                 | Output voltage is 5V when M or H level applied to CTRL pin.  |  |  |  |  |  |

| 6       | COMPOUT                                                                                 | Output for ACC detector.                                     |  |  |  |  |  |

| 7       | ANT CTRL                                                                                | L:ANT output OFF H:ANT output ON                             |  |  |  |  |  |

| 8       | VCC                                                                                     | Connected to VCC.                                            |  |  |  |  |  |

| 9       | BATT DET                                                                                | Low battery detect.                                          |  |  |  |  |  |

| 10      | AUDIO OUT                                                                               | Output voltage is 9V when M or H level applied to CTRL pin.  |  |  |  |  |  |

| 11      | CTRL                                                                                    | L:BIAS OFF M:BIAS ON H:CD ON                                 |  |  |  |  |  |

| 12      | CD OUT                                                                                  | Output voltage is 8V when H level applied to CTRL pin.       |  |  |  |  |  |

| 13      | ILM AJ                                                                                  | Adjustment pin for ILM output voltage.                       |  |  |  |  |  |

| 14      | ILM OUT                                                                                 | Output voltage is 10V when M or H level applied to CTRL pin. |  |  |  |  |  |

| 15      | GND                                                                                     | Connected to GND.                                            |  |  |  |  |  |

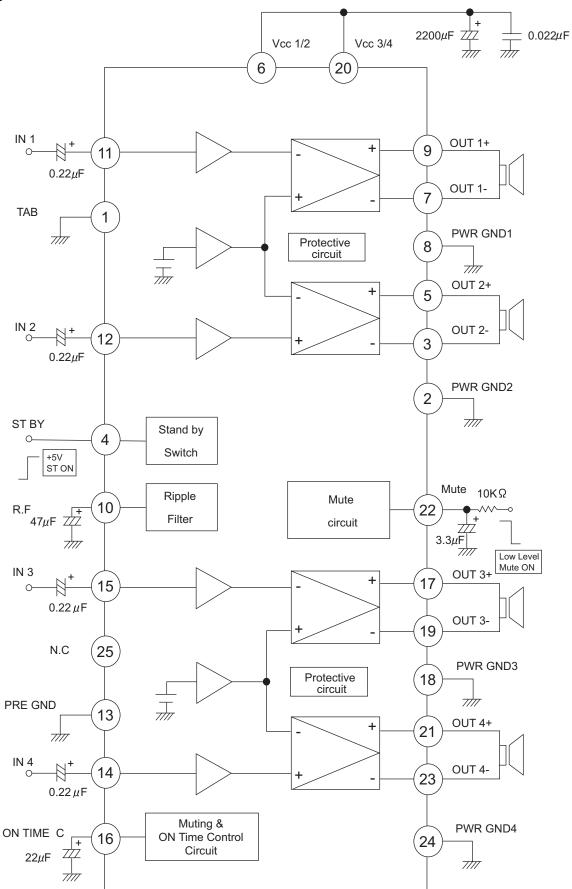

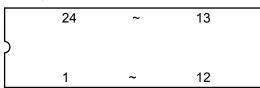

#### 4.2 LA4743K (IC301) : Power amp.

• Pin layout

Pin function

| Pin No. | Symbol | Function                 | Pin No. | Symbol | Function                |

|---------|--------|--------------------------|---------|--------|-------------------------|

| 1       | TAB    | Header of IC             | 14      | FLIN   | Front Lch input         |

| 2       | GND    | Power GND                | 15      | RLIN   | Rear Lch input          |

| 3       | FR-    | Outpur(-) for front Rch  | 16      | ONTIME | Power on time control   |

| 4       | STDBY  | Stand by input           | 17      | RL+    | Output (+) for rear Lch |

| 5       | FR+    | Output (+) for front Rch | 18      | GND    | Power GND               |

| 6       | VP1    | Power input              | 19      | RL-    | Output (-) for rear Lch |

| 7       | RR-    | Output (-) for rear Rch  | 20      | VP3    | Power input             |

| 8       | GND    | Power GND                | 21      | FL+    | Output (+) for front    |

| 9       | RR+    | Output (+) for rear Rch  | 22      | MUTE   | Muting control input    |

| 10      | RIPPLE | Ripple filter            | 23      | FL-    | Output (-) for front    |

| 11      | RRIN   | Rear Rch input           | 24      | GND    | Power GND               |

| 12      | FRIN   | Front Rch input          | 25      | NC     | Non connection          |

| 13      | SGND   | Signal GND               |         |        |                         |

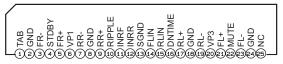

#### 4.3 LA6579H-X (IC561) : 4-Channel bridge driver

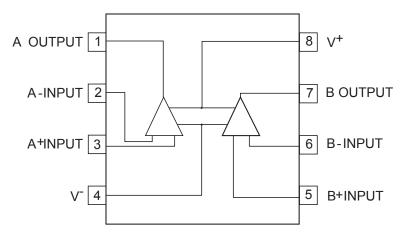

• Pin layout & Block diagram

#### Pin function

| Pin No. | Symbol  | Function                                                         |

|---------|---------|------------------------------------------------------------------|

| 1       | VIN1-A  | CH1 input AMP_inverted input                                     |

| 2       | VIN1+A  | CH1 input AMP_non-inverted input                                 |

| 3       | VCCP1   | CH1 and CH2 power stage power supply                             |

| 4       | VO1+    | Output pin(+)for channel 1                                       |

| 5       | VO1-    | CH1 output pin (-) for channel 1                                 |

| 6       | VO2+    | Output pin(+)for channel 2                                       |

| 7       | VO2-    | Output pin(-)for channel 2                                       |

| 8       | VO3+    | Output pin(+)for channel 3                                       |

| 9       | VO3-    | Output pin(-)for channel 3                                       |

| 10      | VO4+    | Output pin(+)for channel 4                                       |

| 11      | VO4-    | Output pin(-)for channel 4                                       |

| 12      | VCCP2   | CH3 and CH4 power stage powr supply                              |

| 13      | VIN4    | Input pin for channel 4                                          |

| 14      | VIN4G   | Input pin for channel 4(for gain adjustment)                     |

| 15      | VIN3    | Input pin for channel 3                                          |

| 16      | VIN3G   | Input pin for channel 3(for gain adjustment)                     |

| 17      | VIN2    | Input pin for channel 2                                          |

| 18      | VIN2G   | Input pin for channel 2(for gain adjustment)                     |

| 19      | REGIN   | External PNP transistor base connection                          |

| 20      | 3.3VREG | 3.3VREG output pin external PNP transistor, collector connection |

| 21      | VCCS    | Signal system GND                                                |

| 22      | VREFIN  | Reference voltage application pin                                |

| 23      | MUTE    | Output ON/OFF pin                                                |

| 24      | VIN1_SW | CH1 input OP AMP_changeover pin                                  |

| 25      | S_GND   | Signal system GND                                                |

| 26      | VIN1+B  | CH1 AMP_B non-inverted input pin                                 |

| 27      | VIN1-B  | CH1 AMP_B inverted input pin                                     |

| 28      | VIN1    | CH1 input pin input OP_AMP output pin                            |

#### 4.4 LC75823W (IC601) : LCD driver

Pin Layout

| DI<br>CL<br>CL<br>CL<br>CC<br>CC<br>CC<br>CC<br>CC<br>CC<br>CC<br>CC<br>CC<br>CC                                                 |

|----------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                  |

| 64 63 62 61 60 59 58 57 56 55 54 53 52 51 50 49<br>S1 0+1                                                                        |

| 310-1 $40-0.340520-2$ $47-0.547$                                                                                                 |

|                                                                                                                                  |

|                                                                                                                                  |

| S4 0-4 45+0 S45                                                                                                                  |

| $55 \circ -5$ $44 + \circ 544$                                                                                                   |

| $\begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                             |

| $S7 \circ -7$ $42 + \circ S42$                                                                                                   |

| S8 0+8 41+0 S41                                                                                                                  |

| S9 0+9 40+0 S40                                                                                                                  |

| S10 o+10 39 +o S39                                                                                                               |

| S11 o+ 11 38 +o S38                                                                                                              |

| S12 o- 12 37 -o S37                                                                                                              |

| S13 o+13 36 + o S36                                                                                                              |

| S14 o+ 14 35 +o S35                                                                                                              |

| S15 o+ 15 34 +o S34                                                                                                              |

| S16 o+ 16 33 +o S33                                                                                                              |

| 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32                                                                                  |

|                                                                                                                                  |

| 33 33 33 58 74 57 57 57 57 57 58 57 58 57 58 57 58 57 58 57 58 57 58 57 58 57 58 57 58 57 58 58 58 58 58 58 58 58 58 58 58 58 58 |

| ~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~                                                                                           |

#### Pin function

| Pin No.  | Symbol                                                                         |     |                                                                                                                                                             |                                     |  |  |  |  |  |

|----------|--------------------------------------------------------------------------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|--|--|--|--|--|

| 1 to 52  | S1 to S52                                                                      | 0   | egment output pins used to display data transferred by serial data input.                                                                                   |                                     |  |  |  |  |  |

| 53 to 55 | COM1 to COM3                                                                   | 0   | Common driver output pins. The frame frequency is give                                                                                                      | en by : t0=(fosc/384)Hz.            |  |  |  |  |  |

| 56       | VDD                                                                            |     | Power supply connection. Provide a voltage of between                                                                                                       | 4.5 and 6.0V.                       |  |  |  |  |  |

| 57       | ĪNĦ                                                                            | I   | Display turning off input pin.<br>INT="L" (Vss) off (S1 to S52, COM1 to COM3="L"<br>INT="H" (VDD) on<br>Serial data can be transferred in display off mode. |                                     |  |  |  |  |  |

| 58       | VDD1                                                                           | Ι   | Used for applying the LCD drive 2/3 bias voltage externally.<br>Must be connected to VDD2 when a 1/2 bias drive scheme is used.                             |                                     |  |  |  |  |  |

| 59       | VDD2                                                                           | I   | Used for applying the LCD drive 1/3 bias voltage externally.<br>Must be connected to VDD1 when a 1/2 bias drive scheme is used.                             |                                     |  |  |  |  |  |

| 60       | Vss                                                                            |     | Power supply connection. Connect to GND.                                                                                                                    |                                     |  |  |  |  |  |

| 61       | OSC                                                                            | I/O | Oscillator connection.<br>An oscillator circuit is formed by connecting an external                                                                         | resistor and capacitor at this pin. |  |  |  |  |  |

| 62       | CE                                                                             | Ι   | Serial data interface connection to the controller. CE : Chip enable                                                                                        |                                     |  |  |  |  |  |

| 63       | CL                                                                             | I   | Serial data interface connection to the controller. CL : Sync clock                                                                                         |                                     |  |  |  |  |  |

| 64       | 64 DI I Serial data interface connection to the controller. DI : Transfer data |     |                                                                                                                                                             |                                     |  |  |  |  |  |

4.5 NJM4565M-WE (IC571) : CD L.P.F.

#### 4.6 IC-PST600M/G/-W (IC702) : System reset

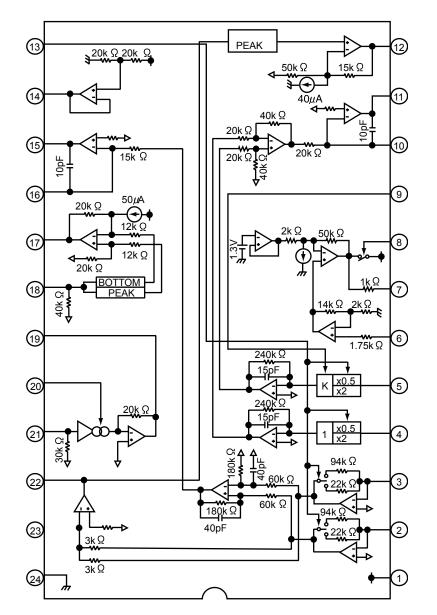

#### 4.7 TA2157FN-X (IC501) : RF amp

Terminal layout

Block diagram

| PIN      | SEL                | TEB      | RFGC       | TEB                   |

|----------|--------------------|----------|------------|-----------------------|

| VCTRLPIN | (APC SW)           | (TE BAL) | (AGC Gian) | (TE BAL)              |

| VCC      | APC ON             | -50%     | +12dB      | Normal mode<br>(0dB)  |

| HiZ      | APC ON             | 0%       | +6dB       | Normal mode<br>(0dB)  |

| GND      | APC OFF<br>(LDO=H) | 50%      | 0dB        | CD-RW mode<br>(+12dB) |

Pin function

| Pin No.  | Symbol       | I/O |                                                                              |                                                                                                                                                                                                                                                                              | Fu            | nction         |                      |                  |  |

|----------|--------------|-----|------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|----------------|----------------------|------------------|--|

| 1        | VCC          | -   | 3.3V power supply pin                                                        |                                                                                                                                                                                                                                                                              |               |                |                      |                  |  |

| 2        | FNI          | I   | Main-beam amp input pin                                                      |                                                                                                                                                                                                                                                                              |               |                |                      |                  |  |

| 3        | FPI          | I   | Main-beam amp input pin                                                      |                                                                                                                                                                                                                                                                              |               |                |                      |                  |  |

| 4        | TPI          | I   | Sub-beam amp input pin                                                       |                                                                                                                                                                                                                                                                              |               |                |                      |                  |  |

| 5        | TNI          | I   | Sub-beam amp input pin                                                       |                                                                                                                                                                                                                                                                              |               |                |                      |                  |  |

| 6        | MDI          | I   | Monitor photo diode amp i                                                    | nput pin                                                                                                                                                                                                                                                                     |               |                |                      |                  |  |

| 7        | LDO          | 0   | Laser diode amp output pi                                                    | n                                                                                                                                                                                                                                                                            |               |                |                      |                  |  |

| 8        | SEL          | I   | APC circuit ON/OFF contro<br>or bottom/peak detection f                      |                                                                                                                                                                                                                                                                              |               | DO) control    | signal input         |                  |  |

|          |              |     | SEL                                                                          | APC<br>circuit                                                                                                                                                                                                                                                               |               | LDO            |                      |                  |  |

|          |              |     | GND                                                                          | OFF                                                                                                                                                                                                                                                                          | Connecte      | d VCC thro     | ugh 1kΩ resistor     |                  |  |

|          |              |     | Hiz                                                                          | ON                                                                                                                                                                                                                                                                           | Control sig   | gnal output    |                      | 1                |  |

|          |              |     | VCC                                                                          | ON                                                                                                                                                                                                                                                                           |               | gnal output    |                      | 1                |  |

| 9        | TEB          | 1   | Adjusts TE signal balance<br>PWM carrier = 88.2kHz)<br>TEBC pin using RC-LPF | Tracking error balance adjustment signal input pin<br>Adjusts TE signal balance by eliminating carrier component from PWM signal (3-state output,<br>PWM carrier = 88.2kHz) output from TC94A14F/FA<br>TEBC pin using RC-LPF and inputting DC.<br>TEBC input voltage:GND~VCC |               |                |                      |                  |  |

| 10       | TEN          | I   | Tracking error signal gene                                                   | ration amp                                                                                                                                                                                                                                                                   | o negative-pł | nase input pii | า                    |                  |  |

| 11       | TEO          | 0   | Tracking error signal gene<br>Combining TEO signal R                         |                                                                                                                                                                                                                                                                              |               | A14F/FA con    | figures tracking sea | arch system.     |  |

| 12       | RFDC         | 0   | RF signal peak detection of                                                  | output pin                                                                                                                                                                                                                                                                   |               |                |                      |                  |  |

| 13       | GVSW         | I   | AGC/FE/TE amp gain cha                                                       | nge pin                                                                                                                                                                                                                                                                      |               |                |                      |                  |  |

|          |              |     |                                                                              |                                                                                                                                                                                                                                                                              | GVSW          | Mode           | ]                    |                  |  |

|          |              |     |                                                                              |                                                                                                                                                                                                                                                                              | GND           | CD-RW          | -                    |                  |  |

|          |              |     |                                                                              |                                                                                                                                                                                                                                                                              |               |                | -                    |                  |  |

|          |              |     |                                                                              |                                                                                                                                                                                                                                                                              | Hiz           | Normal         |                      |                  |  |

|          |              |     |                                                                              |                                                                                                                                                                                                                                                                              | VCC           |                |                      |                  |  |

| 14       | VRO          | 0   | Reference voltage (VRO) (<br>*VRO=1/2VCC When VC                             |                                                                                                                                                                                                                                                                              |               |                |                      |                  |  |

| 15       | FEO          | 0   | Focus error signal generat                                                   | ion amp o                                                                                                                                                                                                                                                                    | utput pin     |                |                      |                  |  |

| 16       | FEN          | Ι   | Focus error signal generat                                                   | ion amp n                                                                                                                                                                                                                                                                    | egative-phas  | se input pin   |                      |                  |  |

| 17       | RFRP         | 0   | Signal amp output pin for t<br>Combining RFRP signal                         |                                                                                                                                                                                                                                                                              |               | C94A14F/FA     | configures tracking  | g search system. |  |

| 18       | REIS         | I   |                                                                              |                                                                                                                                                                                                                                                                              |               |                |                      |                  |  |

| 19<br>20 | RFGO<br>RFGC | 0   | RF signal amplitude adjustment amp output pin                                |                                                                                                                                                                                                                                                                              |               |                |                      |                  |  |

| 20       | N GC         |     | Adjusts RF signal amplit<br>PWM carrier=88.2kHz)ou                           | amplitude adjustment control signal input pin<br>ljusts RF signal amplitude by eliminating carrier component from PWM signal (3-state output,<br>VM carrier=88.2kHz)output fromTC94A14F/14FA *RFGC pin using RC-LPF and inputting DC.<br>GC input voltage:GND~VCC            |               |                |                      |                  |  |

| 21       | AGCIN        | I   | RF signal amplitude adjust                                                   | ment amp                                                                                                                                                                                                                                                                     | input pin     |                |                      |                  |  |

| 22       | RFO          | 0   | RF signal generation amp                                                     | output pin                                                                                                                                                                                                                                                                   | l             |                |                      |                  |  |

| 23       | RFI          | I   | RF signal generation amp                                                     | input pin                                                                                                                                                                                                                                                                    |               |                |                      |                  |  |

| 24       | GND          | -   | GND pin                                                                      |                                                                                                                                                                                                                                                                              |               |                |                      |                  |  |

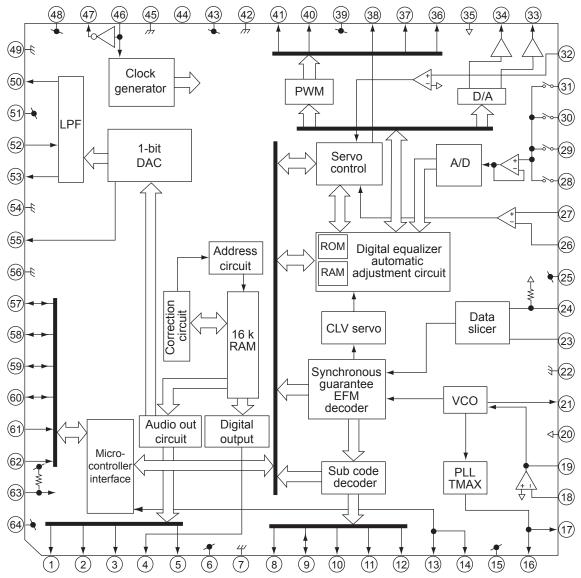

#### 4.8 TC94A14FA (IC521) : DSP & DAC

Terminal layout & block daiagram

#### · Pin function

| Pin<br>No | Symbol           | I/O | Descroption                                                                                              |

|-----------|------------------|-----|----------------------------------------------------------------------------------------------------------|

| 1         | BCK              | 0   | Bit clock output pin.32fs48fsor 64fs selectable by command.                                              |

| 2         | LRCK             | 0   | L/R channel clock output pin."L" for L channel and "H" for R channel.                                    |

|           |                  |     | Output polarity can be inverted by command.                                                              |

| 3         | AOUT             | 0   | Audio data output pin. MSB-first or LSB-first selectable by command.                                     |

| 4         | DOUT             | 0   | Digital data output pin.Outputs up to double-speed playback.                                             |

| 5         | IPF              | 0   | Correction flag output pin. When set to "H" AOUT output cannot be corrected by C2 correction processing. |

| 6         | V <sub>DD3</sub> | -   | Digital 3.3V power supply voltage pin.                                                                   |

| 7         | V <sub>SS3</sub> | -   | Digital GND pin.                                                                                         |

| 8         | SBOK             | 0   | Subcode Q data CRCC result output pin. "H" level when result is OK.                                      |

| 9         | CLCK             | 0   | Subcode P-W data read I/O pin. I/O polarity selectable by command.                                       |

| 10        | DATA             | 0   | Subcode P-W data output pin.                                                                             |

| 11        | SFSY             | 0   | Playback frame sync signal output pin.                                                                   |

| 12        | SBSY             | 0   | Subcode block sync signal output pin. "H" level at S1 when subcode sync is detected.                     |

| 13        | HSO              | I/O | Conorol purpose input / output pine Input port at reset                                                  |

| 14        | UHSO             | 1/0 | General-purpose input / output pins.Input port at reset.                                                 |

| 15        | $PV_{DD3}$       | -   | PLL-only 3.3V power supply voltage pin.                                                                  |

| 16        | PDO              | 0   | EFM and PLCK phase difference signal output pin.                                                         |

1-36 (No.49822)

| Pin<br>No | Symbol              | I/O | Descroption                                                                                                                       |  |  |  |  |

|-----------|---------------------|-----|-----------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 17        | TMAX                | 0   | TMAX detection result output pin.                                                                                                 |  |  |  |  |

|           |                     |     | TMAX Detection Result TMAX Output                                                                                                 |  |  |  |  |

|           |                     |     |                                                                                                                                   |  |  |  |  |

|           |                     |     | Longer than fixed period "PVDD3"<br>Within fixed period "HiZ"                                                                     |  |  |  |  |

|           |                     |     | Shorter than fixed period "AVss3"                                                                                                 |  |  |  |  |

|           |                     |     |                                                                                                                                   |  |  |  |  |

| 18        | LPFN                | Ι   | Inverted input pin for PLL LPF amp.                                                                                               |  |  |  |  |

| 19        | LPFO                | 0   | Output pin for PLL LPF amp.                                                                                                       |  |  |  |  |

| 20        | PVREF               | -   | PLL-only VREF pin.                                                                                                                |  |  |  |  |

| 21        | VCOF                |     | VCO filter pin.                                                                                                                   |  |  |  |  |

| 22        | AV <sub>SS3</sub>   | -   | Analog GND pin.                                                                                                                   |  |  |  |  |

| 23        | SLCO                | 0   | DAC output pin for data slice level generation.                                                                                   |  |  |  |  |

| 24        | RFI                 | Ι   | RF signal input pin. Zin selectable by command.                                                                                   |  |  |  |  |

| 25        | AV <sub>DD3</sub>   | -   | Analog 3.3V power supply voltage pin.                                                                                             |  |  |  |  |

| 26        | RFCT                | 1   | RFRP signal center level input pin.                                                                                               |  |  |  |  |

| 27        | RFZI                | 1   | RFRP signal zero-cross input pin.                                                                                                 |  |  |  |  |

| 28        | RFRP                |     | RF ripple signal input pin.<br>Focus error signal input pin.                                                                      |  |  |  |  |

| 29        | FEI                 | -   | •                                                                                                                                 |  |  |  |  |

| 30        | SBAD                | 1   | Sub-beam adder signal input pin.                                                                                                  |  |  |  |  |

| 31        | TEI                 | 1   | Tracking error input pin. Inputs when tracking servo is on.                                                                       |  |  |  |  |

| 32        | TEZI                |     | Tracking error signal zero-cross input pin.                                                                                       |  |  |  |  |

| 33<br>34  | FOO                 | 0   | Focus equalizer output pin.                                                                                                       |  |  |  |  |

| 34<br>35  | TRO<br>VREF         | 0   | Tracking equalizer output pin.<br>Analog reference power supply voltage pin.                                                      |  |  |  |  |

| 36        | RFGC                | -   | RF amplitude adjustment control signal output pin.                                                                                |  |  |  |  |

| 37        | TEBC                | 0   | Tracking balance control signal output pin.                                                                                       |  |  |  |  |

| 38        | SEL                 |     | APC circuit ON/OFF signal output pin. At laser on, high impedance with UHS="L",                                                   |  |  |  |  |

| 50        | OLL                 | 0   | H output with UHS="H".                                                                                                            |  |  |  |  |

| 39        | AV <sub>DD3</sub>   | -   | Analog 3.3V power supply voltage pin.                                                                                             |  |  |  |  |

| 40        | FMO                 | 0   | Feed equalizer output pin.                                                                                                        |  |  |  |  |

| 41        | DMO                 | 0   | Disc equalizer output pin.                                                                                                        |  |  |  |  |

| 42        | V <sub>SS3</sub>    | -   | Digital GND pin.                                                                                                                  |  |  |  |  |

| 43        | V <sub>DD3</sub>    | -   | Digital 3.3V power supply voltage pin.                                                                                            |  |  |  |  |

| 44        | TESIN               | Ι   | Test input pin. Normally, fixed to "L".                                                                                           |  |  |  |  |

| 45        | XV <sub>SS3</sub>   | -   | System clock oscillator GND pin.                                                                                                  |  |  |  |  |

| 46        | XI                  | Ι   | System clock oscillator input pin.                                                                                                |  |  |  |  |

| 47        | XO                  | 0   | System clock oscillator output pin.                                                                                               |  |  |  |  |

| 48        | $XV_{DD3}$          | I   | System clock oscillator 3.3V power supply voltage pin.                                                                            |  |  |  |  |

| 49        | DV <sub>SS3</sub> R | -   | DA converter GND pin.                                                                                                             |  |  |  |  |

| 50        | RO                  | 0   | R-channel data forward output pin.                                                                                                |  |  |  |  |

| 51        | DV <sub>DD3</sub>   | -   | DA converter 3.3V power supply pin.                                                                                               |  |  |  |  |

| 52        | DVR                 | -   | Reference voltage pin.                                                                                                            |  |  |  |  |

| 53        | LO                  | 0   | L-channel data forward output pin.                                                                                                |  |  |  |  |

| 54        | DV <sub>SS3</sub> L | - ( | DA converter GND pin.                                                                                                             |  |  |  |  |

| 55        | ZDET                |     | 1 bit DA converter zero detection flag output pin.                                                                                |  |  |  |  |

| 56        | V <sub>SS5</sub>    | -   | Microcontroller interface GND pin.                                                                                                |  |  |  |  |

| 57        | BUS0                |     |                                                                                                                                   |  |  |  |  |

| 58        | BUS1                |     | Microsoptrollar interface data I/O pipe                                                                                           |  |  |  |  |

| 59<br>60  | BUS2                | 1/U | Microcontroller interface data I/O pins.                                                                                          |  |  |  |  |

| 60<br>61  | BUS3<br>BUCK        | I   | Microcontroller interface clock input nin                                                                                         |  |  |  |  |

| 61<br>62  | /CCE                | 1   | Microcontroller interface clock input pin.                                                                                        |  |  |  |  |

| 62<br>63  | /CCE<br>/RST        | 1   | Microcontroller interface chip enable signal input pin.At "L", BUS0 to BUS3 are active.<br>Reset signal input pin. At reset, "L". |  |  |  |  |

| 63<br>64  |                     | -   | Microcontroller interface 5V power supply pin.                                                                                    |  |  |  |  |

| 04        | $V_{DD5}$           | -   |                                                                                                                                   |  |  |  |  |

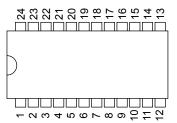

#### 4.9 TB2118F-X (IC31) : PLL

#### • Terminal Layout

· Block diagram

| • | Pin | Function |

|---|-----|----------|

|---|-----|----------|

| Pin<br>No. | Symbol | I/O | Function                                     | Pin<br>No. | Symbol | I/O | Function                             |

|------------|--------|-----|----------------------------------------------|------------|--------|-----|--------------------------------------|

| 1          | XOUT   | 0   | Crystal oscillator pin                       | 13         | IFC    | I   | IF signal input                      |

| 2          | OSC    | -   | Non connect                                  | 14         | VDD    | -   | Power pins for digital block         |

| 3          | CE     | Ι   | Chip enable input                            | 15         | FMIN   | Ι   | FM band local signal input           |

| 4          | DI     |     | Serial data input                            | 16         | AMIN   | I   | AM band local signal input           |

| 5          | СК     | Ι   | Clock input                                  | 17         | DGND   | -   | Connect to GND (for digital circuit) |

| 6          | DOUT   | 0   | Serial data output                           | 18         | FMCP   | 0   | Charge pump output for FM            |

| 7          | SR     | 0   | Register control pin                         | 19         | Vt     | -   | Tuning voltage biased to 2.5V.       |

| 8          | I/01   | I/O | I/O ports                                    | 20         | AMCP   | 0   | Charge pump output for AM            |

| 9          | I/02   | I/O | I/O ports                                    | 21         | VCC    | -   | Power pins for analog block          |

| 10         | OUT1   | -   | Non connect                                  | 22         | RF     | I   | Ripple filter connecting pin         |

| 11         | OUT2   | -   | Non connect                                  | 23         | AGND   | -   | Connect to GND (for analog circuit)  |

| 12         | VDD2   | -   | Single power supply for REF. frequency block | 24         | XIN    | I   | Crystal oscillator pin               |

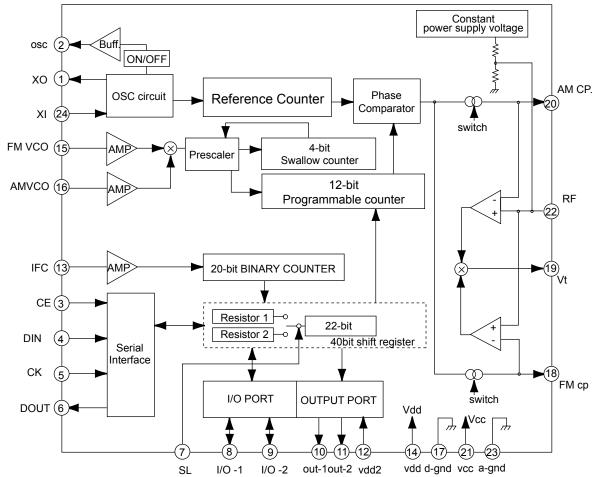

#### 4.10 TEA6320T-X (IC161) : E.volume

Pin layout

| SDA   | 1  | $\bigcirc$ | 32 | SCL   |

|-------|----|------------|----|-------|

| GND   | 2  |            | 31 | VCC   |

| OUTLR | 3  |            | 30 | OUTRR |

| OUTLF | 4  |            | 29 | OUTRF |

| TL    | 5  |            | 28 | TR    |

| B2L   | 6  |            | 27 | B2R   |

| B1L   | 7  |            | 26 | B1R   |

| IVL   | 8  |            | 25 | IVR   |

| ILL   | 9  |            | 24 | ILR   |

| QSL   | 10 |            | 23 | QSR   |

| IDL   | 11 |            | 22 | IDR   |

| MUTE  | 12 |            | 21 | Vref  |

| ICL   | 13 | CD-CH      | 20 | ICR   |

| IMD   | 14 | 00 011     | 19 | CAP   |

| IBL   | 15 | TAPE       | 18 | IBR   |

| IAL   | 16 | TUNER      | 17 | IAR   |

· Block diagram

#### · Pin functions

| Pin<br>No. | Symbol | I/O | Functions                                                                     |

|------------|--------|-----|-------------------------------------------------------------------------------|

| 1          | SDA    | I/O | Serial data input/output.                                                     |

| 2          | GND    | -   | Ground.                                                                       |

| 3          | OUTLR  | 0   | output left rear.                                                             |

| 4          | OUTLF  | 0   | output left front.                                                            |

| 5          | TL     | Ι   | Treble control capacitor left channel<br>or input from an external equalizer. |

| 6          | B2L    | -   | Bass control capacitor left channel or output to an external equalizer.       |

| 7          | B1L    | -   | Bass control capacitor left channel.                                          |

| 8          | IVL    | Ι   | Input volume 1. left control part.                                            |

| 9          | ILL    | Ι   | Input loudness. left control part.                                            |

| 10         | QSL    | 0   | Output source selector. left channel.                                         |

| 11         | IDL    | -   | Not used                                                                      |

| 12         | MUTE   | -   | Not used                                                                      |

| 13         | ICL    | Ι   | Input C left source.                                                          |

| 14         | IMO    | -   | Not used                                                                      |

| 15         | IBL    | Ι   | Input B left source.                                                          |

| 16         | IAL    | Ι   | Input A left source.                                                          |

| Pin<br>No. | Symbol | I/O | Functions                                                                      |

|------------|--------|-----|--------------------------------------------------------------------------------|

| 17         | IAR    | Ι   | Input A right source.                                                          |

| 18         | IBR    | Ι   | Input B right source.                                                          |

| 19         | CAP    | -   | Electronic filtering for supply.                                               |

| 20         | ICR    | I   | Input C right source.                                                          |

| 21         | Vref   | -   | Reference voltage (0.5Vcc)                                                     |

| 22         | IDR    | -   | Not used                                                                       |

| 23         | QSR    | 0   | Output source selector right channel.                                          |

| 24         | ILR    | Ι   | Input loudness right channel.                                                  |

| 25         | IVR    | I   | Input volume 1. right control part.                                            |

| 26         | B1R    | -   | Bass control capacitor right channel                                           |

| 27         | B2R    | 0   | Bass control capacitor right channel<br>or output to an external equalizer.    |

| 28         | TR     | Ι   | Treble control capacitor right channel<br>or input from an external equalizer. |

| 29         | OUTRF  | 0   | Output right front.                                                            |

| 30         | OUTRR  | 0   | Output right rear.                                                             |

| 31         | Vcc    | -   | Supply voltage.                                                                |

| 32         | SCL    | Ι   | Serial clock input.                                                            |

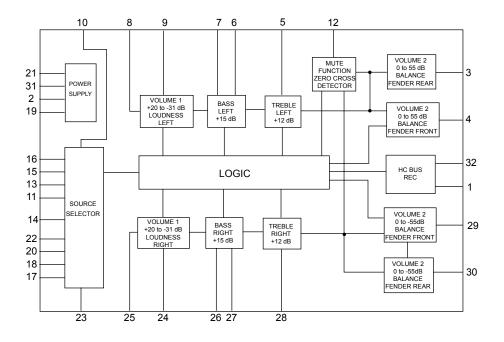

#### 4.11 UPD784215AGC224 (IC701) : CPU

Pin Layout

| 75    | ~ | 51               |

|-------|---|------------------|

| 76    |   | 50               |

| 2     |   | ۲                |

| 100 1 | ~ | 25 <sup>26</sup> |

Pin function

| Pin No. | Symbol    | I/O | function                            |

|---------|-----------|-----|-------------------------------------|

| 1~2     | no use    | 0   | output L                            |

| 3       | SW2       | Ι   | CD mecha SW2                        |

| 4       | PSW       | I   | CD mecha Position Setting SW        |

| 5       | LM        | 0   | loading motor control output        |

| 6       | MOTOR SEL | 0   | Loading/feed motor selecting output |

| 7~8     | no use    | 0   | output L                            |

| 9       | VDD       |     | maicon power supply                 |

| 10      | X2        |     |                                     |

| 11      | X1        |     |                                     |

| 12      | VSS       | -   | GND                                 |

| 13      | XT2       |     |                                     |

| 14      | XT1       |     |                                     |

| 15      | RESET     | I   | SYSTEM RESET                        |

| 16      | SW1       | I   | CD mecha sw1                        |

| 17      | no use    | 0   | output L                            |

| 18      | PS2       | Ι   | power save2, H means STOP mode      |

| 19~22   | no use    | 0   | output L                            |

| 23      | AVDD      |     | A/D converter power supply          |

| 24      | AVREF0    |     | A/D reference voltage               |

| 25      | VOLÇP     | Ι   | volume encoder pulse input 1        |

| 26      | VOLÇQ     | Ι   | volume encoder pulse input 2        |

| 27      | KEY0      | Ι   | key input 0                         |

| 28      | KEY1      | Ι   | key input 1                         |

| 29      | KEY2      | Ι   | key input 2                         |

| 30      | LEVEL     | Ι   | level meter input                   |

| 31      | no use    | Ι   | Input                               |

| 32      | SM        | Ι   | S DMETER input                      |

| 33      | AVSS      | -   | GND                                 |

| 34~35   | no use    | 0   | output L                            |

| 36      | AVREF     |     |                                     |

| 37~40   | no use    | 0   | output L                            |

| 41      | LCD-DA    | 0   | data output for LCD driver          |

| 42      | LCD-SCK   | 0   | CLK output for LCD driver           |

| 43      | LCD-CE    | 0   | CE for LCD driver                   |

| 44      | no use    | 0   | output L                            |

| 45      | E2PROM-DI | Ι   | I2C data input                      |

| 46      | E2PROM-DO | 0   | I2C data output                     |

| Pin No. | Symbol     | I/O | function                                                                                               |

|---------|------------|-----|--------------------------------------------------------------------------------------------------------|

| 47      | E2PROM-CLK | 0   | I2C clock output                                                                                       |

| 48~50   | no use     | 0   | output L                                                                                               |

| 51      | no use     | 0   | output L                                                                                               |

| 53      | SD/ST      | Ι   | station detector or streo indicator input ; H means a station is there. L means the program is stereo. |

| 54      | no use     | 0   | output L                                                                                               |

| 55      | MONO       | 0   | monoral selection output ; H means monoral                                                             |

| 56~60   | no use     | 0   | output L                                                                                               |

| 61      | DETACH     | I   | detach detect input ; H means detaching                                                                |

| 62      | no use     | 0   | output L                                                                                               |

| 63      | SEEK/STOP  | 0   | auto seek and stop selecting output ; H means seeking, L means receiving.                              |

| 64      | IFC CONT   | 0   | IFC control output                                                                                     |

| 65      | FM/AM      | 0   | FM, AM band selecting output ; H = FM CL= AM                                                           |

| 66      | PLL-CE     | 0   | CE output for PLL IC                                                                                   |

| 67      | PLL-DO     | 0   | data output for PLL IC                                                                                 |

| 68      | PLL-CLK    | 0   | clock output for PLL IC                                                                                |

| 69      | PLL-DI     | I   | data input from PLL IC                                                                                 |

| 70      | TEL-MUTING | Ι   | telphone muting detection input ; Active level can be selected H or L in PSM                           |

| 71      | no use     | 0   | output L                                                                                               |

| 72      | VSS        | -   | GND                                                                                                    |

| 73      | no use     | I   | output L                                                                                               |

| 74      | PS1        | Ι   | POWER SAVE1 Çk= ACC off                                                                                |

| 75      | POWER      | 0   | POWER ON/OFF control output H=power on                                                                 |

| 76      | CD-ON      | 0   | CD power supply control output H=CD power on                                                           |

| 77      | MUTING     | 0   | muting output L=muting on                                                                              |

| 78~80   | no use     | 0   | output L                                                                                               |

| 81      | VDD        | -   | maicon power supply                                                                                    |