# MODEL 69431A

OPERATING AND SERVICE MANUAL

FOR CARDS DESIGNATED RUN 1 AND ABOVE\*

\*For Cards above Run 1 a change page may be included.

### SECTION I GENERAL INFORMATION

### 1-1 INTRODUCTION

- This instruction manual contains operating and service instructions for Digital Input Card Model 69431A. The card is designed specifically for use in the 6940A Multiprogrammer and 6941A Multiprogrammer Extender units to receive 12 separate digital logic-level inputs from a user's external device. As shipped from the factory, the inputs to the 69431A card can be either negative-true (Option 069) or positive-true (Option 073) microcircuit logic levels or open collector negative-true (Option 070) logic levels. In addition to the 069, 073, and 070 options, the digital input card can also be modified to satisfy a wide variety of custom interface requirements such as relay contact closure logic inputs as necessary. Input bias networks and/or option jumpers can be selected either at the factory or by the user to interface the user's specific logic sense and voltage polarity input requirements.

- 1-3 Overall system concepts, including system installation, troubleshooting, and operating considerations are covered in the instruction manual for the 6940A master unit and are not repeated in this manual.

#### 1-4 OPTION 069

1-5 Option 069 is employed for inputs having negative-true logic sense (0 volt input for programmed binary 1) and microcircuit logic levels (0 to +5 volts). As supplied from the factory, the jumper connections on the digital input card are configured such that the logic sense requirements of the input data bits and flag signal as well as the gate signal output are as follows:

DATA BIT INPUTS: LO - TRUE

GATE OUTPUT: HI-to-LO transition

FLAG INPUT: HI-to-LO transition - BUSY LO-to-HI transition - READY

Other input and output signal senses can be accommodated by adding or removing jumpers on the digital input card (see Section III).

#### 1-6 OPTION 073

1-7 Option 073 is employed for inputs having positive-true logic sense (+5 volt input for programmed binary 1) and microcircuit logic levels (0 to +5 volts). As supplied from the factory, the jumper connections on the digital input card are

configured such that the logic sense requirements of the input data bits and flag signal as well as the gate signal output are as follows:

DATA BIT INPUTS: HI - TRUE

GATE OUTPUT: HI-to-LO transition

FLAG INPUT: HI-to-LO transition - BUSY

LO-to-HI transition - READY

Other input and output signal senses can be accommodated by adding or removing jumpers on the digital input card (see Section III).

#### 1-8 OPTION 070

1-9 Option 070 is employed for inputs derived from open-collector output drivers having negative-true logic sense and logic levels up to +14V. As supplied from the factory, the jumper connections on the digital input card are configured such that the logic sense requirements of the input data bits and flag signal as well as the gate signal output are the same as for Option 069. Again, the jumper options allow for other logic senses to be accommodated (see Section III).

#### 1-10 STORAGE DISABLE

1-11 Option jumper W10 is provided to allow input data to be: (1) stored on the input card at the READY transition of the user's FLAG input (trailing edge) or (2) continually available on the input card as received on the input data lines. As shipped from the factory, W10 is installed and input data storage requires the trailing edge of the FLAG input. The user can disable the storage requirement by removing the W10 jumper.

### 1-12 DESCRIPTION

- 1-13 When installed in a Multiprogrammer System, the digital input card is programmed by a 16-bit address word originating at a remote computer or the 6940A Multiprogrammer control panel. The twelve least significant bits of the programmed bits (bits 0-11) are not relevant to the input card and are not used while the remaining four bits (bits 12-15) contain the slot address of the input card.

- 1-14 When the input card slot is addressed by the computer or from the control panel, 12-bit input data contained in its storage circuits is transferred to the computer or 6940A multiprogrammer control panel if the multiprogrammer has been previously placed in the input select (ISL) mode.

1-15 With W10 installed, the digital input card stores 12-bit input data from the user's device when the device supplies a Flag ready (trailing edge) input in response to a Gate signal supplied to the device from the digital input card. The input card gate/flag circuit is controlled by the remote computer or from the 6940A control panel and is activated (the gate signal is generated) either: (1) selectively when the input card is addressed and strobed after the Multiprogrammer System has been placed in the ISL mode or (2) in conjunction with other input cards when the multiprogrammer is placed in the IEN mode. The second method of activation (IEN) requires that a jumper option be installed on the input card.

1-16 In addition to processing the device gate/ flag signals to control data input, the input card gate/flag circuits also develop, in conjunction with input card control circuits, timing flag and input request signals for application to the computer. The timing flag signal is generated either when the card is addressed and in the data-ready state or when the multiprogrammer has been previously placed in the interrupt enable (IEN) mode and the card is activated and in the data ready state. The timing flag signal is combined in the multiprogrammer with all other input (and output) card timing flag signals into the common (combined) timing flag (CTF) signal used by the multiprogrammer in the timing mode to signal to the computer when data is ready for input (or output). The input request (IRQ) identification signal is generated when the card is addressed, activated, and in the data ready state. Like the CTF signal, the IRQ signal is combined in the multiprogrammer with input request identification signals from all other input cards. Further, the combined IRQ signal is incorporated into bit 15 of the data returned to the computer when an input card is addressed. Note that the common timing flag and IRQ signals are also applied to the 6940A Multiprogrammer control panel during the local programming mode of operation.

1-17 The digital input card also contains a control circuit that is involved (with the gate/flag circuits) in developing the common timing flag and input re-

quest identification signals. The control circuit stores the activation status of the input card in that when the card's gate/flag circuits are activated, the control circuit is set to the active state. The control circuits remain active and allow the gate/ flag circuits to generate the common timing flag and input request signals. When the card is deactivated, the CTF signal is partially disabled while the IRQ signal is completely turned off. The control circuits are activated when the gate/flag circuits are activated; that is, when the card is addressed and strobed in the ISL mode. The control circuits are deactivated if the card is addressed and strobed when the ISL mode is off. When deactivated, the control circuits inhibit the input card's CTF signal during the IEN mode and, also, inhibit completely the input request signal. Note, however, that CTF can still be generated by addressing the card when it is in the data ready state.

1-18 The data storage and gate/flag operation of the digital input card described above can be modified at the option of the user. For instance, if the user does not have a flag timing circuit, a hardware jumper can be removed from the input card to disable the device flag trailing edge data storage requirement of the input card so that the user's 12-bit input data will be entered into the card storage circuits as received from the device. On the other hand, the storage circuits can be utilized even if the user does not have a flag timing circuit by jumpering the input card gate output and flag input connections.

1-19 The input card is fabricated on a  $4\frac{1}{2}$ " x 11" printed circuit card. The inner edge of the card contains a dual 24 pin (48 pin total) printed circuit plug that can mate with any connector in slot 400 through 414 of a multiprogrammer unit (6940A or 6941A). A dual 15-pin (30-pin total) printed circuit plug located on the outer-edge of the card connects the 69431A to the external device.

### 1-20 SPECIFICATIONS

1-21 Table 1-1 provides detailed specifications for the Model 69431A.

Table 1-1. Model 69431A Specifications

DATA OUTPUT (To Computer): 12-bit binary

Options 069 and 070: binary 1 = input in LO

state

binary 0 = input in HI

state

Option 073: reverses above relation—

ships

DATA INPUT (From Device) LEVELS: 12-bit binary

Options 069 and 073: LO = 0 to 0.8V (6mA max.

SINK CURRENT)

HI = 2.0V to 5.0V (1ka

source impedance)

Option 070: (open collector drivers)

LO = 0V to 1.0V (15mA

max. sink current)

HI = +6V to +14V

User-Connected Options: receiver input bias network and gate can

be modified to accommodate wide range of inputs.

### INPUT DATA STORAGE:

Standard (Options 069, 070, 073):

12-bit storage register receives input data at end-of-FLAG transition of external device FIAG input. Data must be at specified level when end-of-FLAG received and remain for 3µsec (min.).

#### User-Selected Option:

User can disable data storage by removing option jumper. Data available at card as received on input data lines.

### DEVICE COMMAND (GATE) OUTPUT:

Standard (Options 069, 070, 073):

One normally HI logic level line. HI-to-LO change in level indicates data is requested by input card. Level normally reverts to original status (HI) at start of external device response (FLAG). User can select option to revert level to HI at end of external device response.

### User-Selected Option:

One normally LO logic level line, LO-to-HI change in level indicates data is requested by input card. Level normally reverts to original status (LO) at start of external device response (FLAG). User can select option to revert level to LO at end of external device response.

### Gate Output Level:

. Options 069 and 073: LO = saturation;  $50_{\Omega}$ max. (11mA max.

sink current)

$HI = cutoff, lk_{\Omega} (max.)$

Option 070: LO = saturation;  $50_{\Omega}$ max. (40mA max.

sink current)

$HI = cutoff, 10k_{\Omega} (max.)$

Should not be set to data requested state twice in succession (i.e. before it is reset by FIAG).

#### DEVICE SIGNAL (FLAG) INPUT:

Minimum pulse width: 2µsec

Minimum rise and fall times: 0.1V/usec

Standard (Options 069,070,073):

One normally HI input line. HI-to-LO change in level indicates external device is busy processing data in response to device command (gate) output. End-of-FLAG (LO-to-HI transition) indicates device data available to input card.

User-Selected Option: One normally LO input line. LO-to-HI change in level indicates external device is busy processing data in response to device command (gate) output. End-of-FLAG (HI-to-LO transition) indicates device data available to input card.

If external FIAG input not desired, GATE output can be connected directly to FLAG input or left open (see INPUT DATA STORAGE).

FLAG input level: Same as DATA INPUT LEV-ELS

TEMPERATURE RANGE: 0°C to +80°C operating in mainframe (allows +25°C internal rise when operating in mainframe at up to +55°C ambient).

-40°C to +80°C storage.

### OPERATING POSITION: Any (no restrictions)

#### INPUT CONNECTOR:

One 15-pin dual (30-pin total) edge connector. Mating female connector assembly supplied (HP Part No. 5060-7934).

#### DIMENSIONS:

4.5" x 11.0" nominal

### WEIGHT:

0.7 lbs.

### 1-22 INTERFACING

1-23 The 69431A Digital Input Card is automatically interfaced with its associated multiprogrammer unit when it is installed in a 400 series slot connector. Once it is assigned to a slot, the card

assumes the address of that position and will input data only when the applicable unit and slot are addressed. All operating power and address data for the card are derived from the multiprogrammer unit.

1-24 Interfacing considerations involving the

69431A and the external device are covered in detail in Section III of this Instruction Manual.

1-25 OUTPUT CONNECTOR ASSEMBLY

1-26 One 30-pin output connector assembly (HP Part No. 5060-7934) is furnished with each digital input card for interfacing the card with the external system. Additional 30-pin connector assemblies may be ordered from your local Hewlett-Packard sales office (refer to list at rear of manual for ad-

dresses).

### 1-27 ORDERING ADDITIONAL MANUALS

1-28 Two manuals are shipped with each 69431A order. Additional manuals may be purchased from your local Hewlett-Packard field office (see list at rear of this manual for addresses). Specify the card model number and HP Part Number shown on the title page.

# SECTION II INSTALLATION

### 2-1 INITIAL INSPECTION

2-2 Before shipment, the 69431A Digital Input Card was inspected and found to be free of mechanical and electrical defects. As soon as the card is received, proceed as instructed in the following paragraphs.

### 2-3 MECHANICAL CHECK

2-4 If external damage to the shipping carton is evident, ask the carrier's agent to be present when the card is unpacked. Check the card for signs of physical damage. If it is damaged, file a claim with the carrier's agent and notify Hewlett-Packard Sales and Service Office as soon as possible. If it appears to be undamaged, perform the electrical check specified in the following paragraph.

### 2-5 ELECTRICAL CHECK

2-6 Check the electrical performance of the output card as soon as possible after receipt. Section V of this manual contains checkout procedures which will verify operation of the card. Refer to the inside front cover of this manual for Certification and Warranty statements.

### 2-7 REPACKING FOR SHIPMENT

2-8 When shipping an input card, it is recommended that the package designed for it be used. The original packaging material is reusable. If it is not available, contact your local Hewlett-

Packard field office to obtain the materials. This office will also furnish the address of the nearest service office to which the input card can be shipped. Be sure to attach a tag to the card specifying the owner, model number, and service required, or a brief description of the trouble.

### 2-9 INPUT CARD INSTALLATION

- 2-10 Input cards are installed in slots 400 through 414 of a Multiprogrammer unit. To install an input card, proceed as follows:

- a. Open the hinged front panel of the Multiprogrammer unit by turning the recessed screw within the knurled handle counterclockwise.

- b. With the extractor handle on the top and the card components on the right, slide the card into the desired multiprogrammer slot (400 through 414). Note that all input cards are slotted between pins 4 and 5 and all 400 series connectors of the Multiprogrammer are keyed between the same points. This makes it virtually impossible to plug an input card in upside down or into any slot other than a 400 series slot.

- c. Route all wiring from the input cards through the false-bottom channel and out the back of the unit to the external system.

- d. As physical installation and wiring are completed for the input card, carefully note and record the following types of information on the installation record card located on the rear of the hinged front panel of the multiprogrammer.

- (1) Input card type

- (2) Application in external system

- (3) Timing flag period, logic sense, etc.

# SECTION III OPERATING INSTRUCTIONS

### 3-1 MULTIPROGRAMMER CONNECTIONS

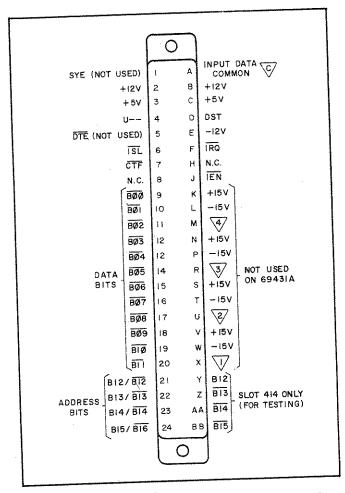

3-2 The Digital Input Card is controlled by the multiprogrammer unit in which it is installed. All dc operating power, address bits, and control signals are supplied to the input card through multiprogrammer main frame connectors in slots 400 through 414. Figure 3-1 illustrates the signals present on all multiprogrammer 400-series connectors. Notice that several signals (i. e. SYE, DTE, etc.) are used only by multiprogrammer output cards and are not utilized in the Digital Input Card.

### 3-3 PROGRAMMING

- 3-4 The programming information presented here defines the relationships of programmed data and the 69431A card outputs to the computer. Complete system programming instructions are given in the Operating and Service manual for the 6940A Multiprogrammer. Since the digital input card has been designed to provide a wide range of flexibility in interfacing the user's device to the computer via the multiprogrammer system, no attempt has been made in this programming information to be definitive of all the ways in which an input card can be used in a system. Rather, the intent has been to describe general programming considerations applicable to the card and to indicate the broad flexibility of usage provided by the digital input card.

- 3-5 Generally, the digital input card is operated in two typical modes of operation as defined in the multiprogrammer by the controlling computer. One mode, the dedicated input mode, is utilized in simple data input sequences and requires that the card be addressed during the data transfer cycle between the card and external device as a condition for allowing the card to signal the computer that data is ready from the external device. The other mode of operation, the interrupt search input mode, is utilized in more complex data input sequences involving many input cards (up to 240, the maximum possible complement of multiprogrammer system input cards) that are simultaneously active in data transfer cycles with their associated external devices. The interrupt search input mode does not require that the computer address the input card during the data transfer cycle as a condition for allowing the card to signal the computer that data is ready for input. Instead, all cards are allowed to signal the computer when the data transfer cycle is over (as soon as data is available) with the com-

Figure 3-1. Multiprogrammer 400 Series Slot Connector

puter responding by searching for the card (from among the active group) which signalled that it was ready. The procedures required for programming the digital input card in the two modes of operation are described below.

### 3-6 DEDICATED INPUT MODE

- 3-7 There are four general steps involved in programming a digital input card for dedicated input mode of operation:

- a. Programming the multiprogrammer into the input select (ISL) mode in order to convert the multiprogrammer into an input device and to enable the input card to be activated. Further, prior to card activation, the multiprogrammer is normally placed

in the timing mode (TME) to allow the input card's flag circuit to control the multiprogrammer flag to the computer. Note that if the card is operated in the handshake mode (TME off) during dedicated input operation, the card should not be activated (Step b. below) twice before the external device has responded with the FLAG ready indication. These initial conditions require a multiprogrammer control word.

- b. Activating the input card by addressing and data strobing the card. This will generate a GATE signal to the external system. Note that card addressing actually requires two operations: first, the unit in which the input card is installed must be specified in a multiprogrammer control word. Next, the input card's slot address must be specified in a multiprogrammer address word. Further, the card address must be maintained to allow the card to signal it is ready with data.

- c. Inputting card data when the input card signals that it is ready. Since the card address is maintained by the computer to allow the card to signal data ready, the card's data is available to the computer as soon as the data ready signal is received.

- d. Activating the card again (Step b.) for the next data input or deactivating the card by first programming the input select mode off and then addressing and strobing the card.

### 3-8 INTERRUPT SEARCH INPUT MODE

- 3-9 There are seven general steps involved in programming a digital input card for interrupt search input mode of operation:

- a. Programming the multiprogrammer into the input select mode as in Step a. (above). However, card activation in the search mode is usually done with the multiprogrammer in the "fast" (handshake) mode (TME is off).

- b. Activating all desired input cards by addressing and data strobing each card.

- c. Programming the multiprogrammer into the interrupt enable mode (IEN) in which the computer's multiprogrammer I/O channel will wait for one of the activated input cards to signal that data is ready. This step requires a multiprogrammer control word having both IEN and TME programmed on.

- d. When an input card completes the data transfer cycle with its external device, it signals the computer that data is ready. The computer should respond by entering the interrupt search routine. First, the computer programs the interrupt enable mode off (to prevent other input cards from signalling data ready) and the input select mode on (in order to communicate with the input cards by turning the multiprogrammer back into an input device). The timing mode is usually turned off also to allow rapid input card data search. This step also requires a multiprogrammer control word.

- e. Next, the multiprogrammer searches for

- the data ready card by addressing the cards (in a software-established priority) one at a time and inputting card data. The data search is usually done without strobing the card so as to avoid reactivating a currently busy card (one that had <u>not</u> signalled data ready).

- f. In addition to the 12 data bits received from each input card when addressed, the input cards also return an indication of their data ready status to the computer in the bit 15 line of the data bits returned to the computer from the multiprogrammer. The computer next examines (by software) this bit to determine if the accompanying data bits are valid (i.e. the card had signalled it was ready for data input).

- g. After detecting and reading the ready card, the computer should reactivate (Step b.) or deactivate the card (address and strobe the card after turning ISL off) depending on whether or not more data is expected. The computer then can turn the interrupt enable mode back on (Step c.) or not as desired.

- 3-10 The digital input card includes an optional jumper (W6) that is installed at the factory and allows Steps 3-9a and 3-9b to be bypassed. All cards having the W6 jumper installed are simultaneously activated when the interrupt enable mode is programmed (Step c.). Note that since IEN is turned off (Step d.) and back on (Step h.) again as part of the interrupt search input mode, circuits on the input card prevent a previously-activated and/or still-busy input card from being activated when IEN is programmed. Thus, the input cards can also be activated selectively as described above. Programming data transfers after installing the W6 jumper can be done as follows:

- a. Activate all cards with W6 installed by programming the interrupt enable mode (IEN and TME are on).

- b. As each card times out, search for the data ready card, read in the data, and deactivate the ready card.

- c. After all cards have timed out, been read, and deactivated, reactivate all cards again by repeating Step a. If no more data is expected, leave all cards deactivated. Note that the procedure above treats the input cards as a group so that the W6 jumper provides an especially handy tool for rapidly communicating with devices having similar data transfer rates in which they all will time out at around the same time after activation and can be read at that time after which they all can again be reactivated for the next data cycle.

- 3-11 It is assumed in the following discussion that the reader is familiar with the definitions and functions of multiprogrammer control and address words. If this is not the case, it is suggested that Section III of the 6940A Instruction Manual be reviewed before proceeding.

3-13 The DST line is wired to all multiprogrammer 400 series slots. The DST line goes HI when the computer gate input to the multiprogrammer goes true and stays HI for the length of the computer gate. The computer gate is set by the computer but is reset by the multiprogrammer flag back to the computer (when the flag goes busy). If the multiprogrammer is in the timing mode (TME on) and the interrupt enable mode is off (IEN off), the multiprogrammer flag is controlled by a combination of the multiprogrammer timing circuits and the input/output card Common Timing Flag (CTF) circuits. In this case, the multiprogrammer flag goes busy and resets the computer gate (and; thus, resets the DST line) a short time after the DST signal goes HI (the multiprogrammer flag ready state will be entirely controlled by the card Common Timing Flag circuits, however). When the IEN mode is on along with the TME mode, however, the multiprogrammer flag does not go busy after DST to reset the computer gate and DST. Instead, the multiprogrammer flag follows the input cards' CTF line and goes busy to reset the computer gate (and, therefore, DST) only when an input card CTF line goes busy. Note that since all input and output cards generate CTF outputs, all output cards should be allowed to time out before programming the interrupt enable mode (IEN and TME on). If the multiprogrammer is in the fast (handshake) mode (TME off), on the other hand, the multiprogrammer flag to the computer is set busy (as it is for TME on with IEN off) a short time after the DST line goes HI. Thus, depending upon the state of IEN and/or TME, the DST signal is either a short duration pulse used to strobe the input cards or it is a level used to control the input card timing circuits (i.e. in the interrupt enable mode).

- 3-14 The DST signal is generated for each multiprogrammer control word and notifies the multiprogrammer to store the control word mode of operation specifications. The DST signal is <u>not</u>, however, required for input card address words. If the DST signal is provided in an address word, its affect depends on the state of the multiprogrammer input select (ISL) mode as follows:

- a. If ISL was programmed on prior to the address word and DST, the data strobe causes the input card to be activated. This means that the input card GATE to the external device will be generated to notify the device that data is requested and to start the data transfer cycle. In addition, the input card control circuits will be set to store the fact that the input card was activated.

- b. If ISL was programmed off prior to the address word and DST, the data strobe resets the input card control circuits and the card is, therefore, deactivated. When deactivated, the input card cannot signal that data is ready in the interrupt

enable mode (the card could still signal ready if operated in the dedicated input mode; i.e. if the card is addressed after it is activated and subsequently deactivated).

### 3-15 INPUT SELECT (ISL)

3-16 The ISL line is wired to all multiprogrammer 400 series slots but is only utilized by cards having input capability. Within the multiprogrammer, ISL reverses the direction of data flow and allows data from an addressed input card to be sent to the computer. In addition, ISL causes the multiprogrammer to combine an addressed input card's input request identification signal (IRQ) with bit 15 of the return data lines for application to the computer. At the input card, ISL enables the card to be activated (if the card is addressed and the data strobe is generated as discussed above).

#### 3-17 CARD ADDRESSING

3-18 An input card is selected to transmit data and/or activate/deactivate when its associated address bits (B12/B12 through B15/B15 and a unit select line U--) are all HI. Although both the true and complemented forms of the address bits are represented on Figure 3-1, only one of the two states is present on each of the four address gate lines when the card is installed in a multiprogrammer slot. For example, if the input card is installed in slot 405, then bits B12(1),  $\overline{B13}(2)$ , B14(4), and B15(8) will be present on the address lines, and all four lines will be HI when the associated multiprogrammer unit is selected as part of a control word. The unit selection is stored in the 6940A and remains in effect until a different unit is selected by a subsequent control word.

3-19 In addition to enabling data transfer to the computer, the card address is also required during the dedicated input mode of operation to allow the card to signal when it has data ready (assuming, of course, that the card was activated and its external device times out). The card address is also required to enable a data ready card to apply its IRQ signal (which is combined with return data bit 15) to the multiprogrammer main frame providing the input card is ready and the control circuits are in the active state (and ISL is on in the main frame).

### 3-20 INTERRUPT ENABLE (IEN) MODE

3-21 The IEN line is wired to all-multiprogrammer 400 series slots but is only utilized by cards having input interrupt capability. When programmed in a control word, IEN enables previously activated input cards to signal the computer when data is ready (assuming, of course, that the card's control circuits are in the active state). In addition, assuming jumper W6 is not removed, IEN activates

the input card(s) providing the card is not currently busy and had not been previously set to the active state. If the card is busy or its control circuits are already set active, the card is not activated when IEN is programmed and the card's GATE to the device is not set.

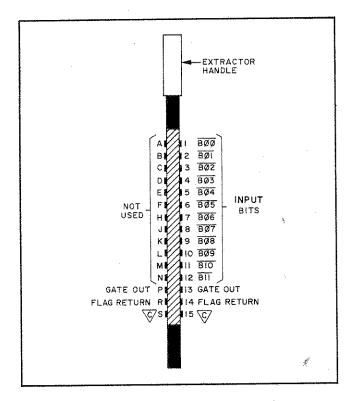

### 3-22 INPUT BITS $\overline{B00}$ THROUGH $\overline{B11}$

3-23 Input Data Transfer. Option jumper W10 is installed on the input card at the factory, so that external device input bits B00 through B11 are stored in the digital input card storage register when the card receives the trailing edge of the external device flag input. If ISL and the card address has been programmed, the stored bits will be transferred to the computer (via the multiprogrammer main frame) through the output logic gates. If storage disable jumper W10 is removed, the flag trailing edge is not required so that input data appears at the output logic gates as received from the device. Figure 3-2 shows the pin numbers on the digital input card input connector to which the input bits can be applied.

Figure 3-2. 69431A Input Connector

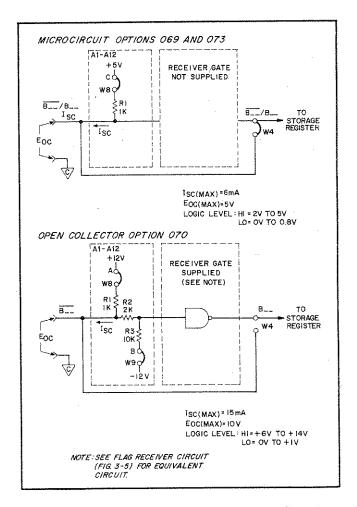

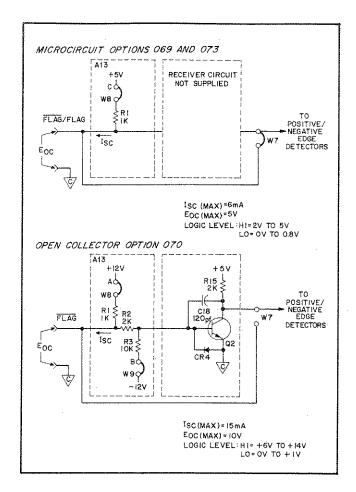

3-24 <u>Input Bit Levels</u>. The digital input card is supplied from the factory to accommodate negative-or positive-true logic sense TTL/DTL microcircuit logic level data inputs (Options 069 and 073, respectively) as well as negative-true open collector data inputs (Option 070). Figure 3-3 depicts the

receiver circuits employed for the three options. As shown, for the microcircuit logic level options, a 1k pullup resistor (R1) is provided in the input circuit and the data input is jumpered through W4 (installed for these options) to the storage register. For the 073 option, an input bias network (R1, R2, and R3) is supplied as well as a level conversion gate (hybrid IC) the combination of which changes the open collector logic levels to the microcircuit levels used in the input card and multiprogrammer. Notice that, as required by the user, the input card receiver circuits can be custom modified (at the factory or by the user) to accommodate other logic sense and logic level requirements.

Figure 3-3. Typical Data Bit Receiver Circuit

### 3-25 GATE

3-26 The input card gate signal notifies the external device that the input card is ready for data. The GATE signal is generated when the input card is activated as discussed previously. Depending upon option jumpers W1 and W2, the GATE signal is reset either when the external device responds to the GATE by setting the FLAG input to the busy

state (leading edge) or at the ready state of the FLAG input (trailing edge). See Table 3-1 for a summary of jumper connections required to select either leading or trailing edge GATE reset. In addition to initiating the data transfer cycle with the external device, the GATE signal, when set, also resets the input card Flag flip-flop. If the input card is in the dedicated input mode (the card address is enabled), the reset state of the Flag flip-flop causes the input card CTF output to go LO (which signals the computer that the input card is busy).

Table 3-1. GATE and FIAG Timing Options

| FLAG JUMPER<br>CONNECTIONS |     | GATE TIMING RELATIVE TO DEVICE FLAG                                                                                 |

|----------------------------|-----|---------------------------------------------------------------------------------------------------------------------|

| W 1                        | W 2 | DEVICE I LAG                                                                                                        |

| Α*                         | ₽*  | GATE RESET AT START OF FLAG (W7 IN)  FLAG (W7 OUT)                                                                  |

| А                          | А   | GATE RESET AT END OF FLAG (W7 IN) DATA READY  FLAG (W7 OUT)                                                         |

| B**                        | A** | GATE RESET AT START OF FLAG (W7 OUT) FLAG (W7 IN)  GATE RESET AT START OF FLAG (GATE RESET AT START OF FLAG (W7 IN) |

| . В                        | В   | GATE RESET AT END OF FLAG (W7 OUT)  FLAG (W7 IN)                                                                    |

<sup>\*</sup> JUMPERS CONNECTED IN THESE POSITIONS AT THE FACTORY FOR OPTIONS 069 AND 073.

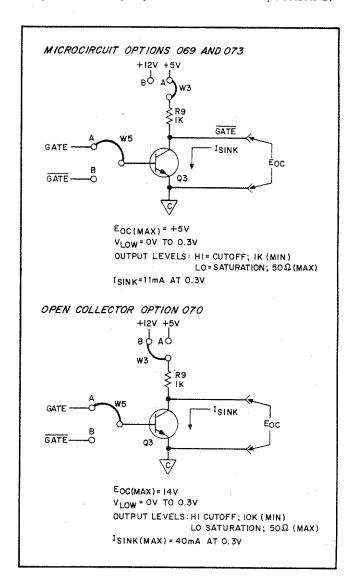

3-27 The GATE output of the input card is produced by the driver circuit depicted in Figure 3-4. As shown, two jumpers, W5 and W3, are provided in

the driver circuit to allow either negative—or positive—true logic sense (jumper W5) and/or microcircuit or higher logic level output (jumper W3). Jumper W5 is connected at the factory to the A position which selects the positive—true state of the GATE signal for application to the gate driver. After inversion by the driver, the negative—true GATE output is applied to the external circuit. If the user desires positive—true GATE output, he must connect the W5 jumper to the B position. Similarly, the W3 jumper is connected to position A to provide microcircuit logic level output. For higher logic level output, the W3 jumper is connected to position B.

Figure 3-4. GATE Driver Circuit

### 3-28 FLAG

3-29 The external device signals when it is busy or ready with data via the device FLAG input to the input card. The leading edge of the FLAG signals

<sup>\*\*</sup> JUMPERS CONNECTED IN THESE POSITIONS AT THE FACTORY FOR OPTION 070.

the input card that the external device is busy processing data (in response to the input card GATE signal to the device). The busy transition of the FIAG input (leading edge) can be selected to reset the input card GATE output in preparation for the next data transfer cycle (card activation). The GATE can also be reset with the trailing edge (data ready) of the FIAG. Refer to Table 3-1 for a summary of jumper connections required to select either leading or trailing edge GATE reset.

3-30 The trailing edge of the FLAG input is also used to notify the input card that data is available from the external device. If jumper W10 is installed, the ready transition of the FLAG strobes the data into the input card storage circuit. Data must be available on the input connector for 3µsec after the FLAG reaches the ready logic level. Further, the rising and falling edges of the FIAG must be  $\geq 0.1 \text{V}/\mu\text{sec}$  (thus, a 3.5V to 0V FIAG transition must reach approximately OV within 35µsec). In addition to data strobing, the trailing edge of the FLAG sets the input card Flag flip-flop to the ready state. If the input card is in the dedicated input mode (the card address is enabled), the CTF output is switched to HI at this time to notify the computer that data is ready. If the input card is in the interrupt search input mode (IEN is on, DST is HI and the card has been activated), the ready state of the input card causes the  $\overline{\text{CTF}}$  output to go LO. In this mode, the LO state of CTF causes the computer gate to reset which, in turn, resets the multiprogrammer DST signal. When reset, the DST signal switches the input card's CTF output HI to notify the computer that data is ready.

3-31 The device FLAG input passes through a receiver circuit that is comprised of discrete components but has identical specifications as the data bit receiver circuits previously described (see Figure 3-5). The Flag receiver circuit allows negative- or positive-true logic sense FLAG inputs to be utilized as well as open-collector inputs. The W7 jumper (which is comparable to the data bit W4 jumpers) is installed for microcircuit logic level inputs (Option 069 and 073) and applies the FLAG input directly to the input card logic circuits. The W7 jumper is removed for the open collector FLAG input thus allowing an input bias circuit and inverter to be installed in order to convert the input to the microcircuit logic level.

### 3-32 GATE/FLAG TIMING

\* 15 of

3-33 The W1 and W2 jumpers, in conjunction with the W7 jumper, allow the input card GATE to the external device to be reset with either the leading or trailing edge of the device FIAG input. In addition, the W1 and W2 jumpers are selected so that the trailing edge of the FIAG input strobes data into the input card storage circuits (assuming jumper

Figure 3-5. Flag Receiver Circuit

W10 is installed so that the data storage strobe is required). Further, the FIAG trailing edge sets the input card Flag flip-flop to the data ready state. Table 3-1 summarizes the GATE/FLAG timing relationships that can be selected by changing the Wl and W2 connections. The table assumes that the negative-true GATE output to the external device is selected (W5 connected to position A). The timing relationships apply equally if positive-true GATE is used (W5 connected to position B). The table lists the W1 and W2 connections required for microcircuit logic level FLAG inputs (W7 is installed) or for other than microcircuit logic level FLAG inputs (i.e. if open collector logic is used in which case W7 is removed and the FLAG receiver circuit is employed). For example, as shown in the table, if a negative-true open collector FLAG input is used and the GATE is to be reset on the trailing edge, the W1 and W2 jumpers must be both connected to position B (the W7 jumper is, of course, removed.).

### 3-34 CABLE FABRICATION

3-35 Since the Digital Input Card may be used to interface with various external devices, an interconnecting cable must be prepared for the particular

device being used. A 30-pin connector is furnished with each Digital Input Card for this purpose. Figure 3-2 illustrates the signals and associated connector pin numbers of the Digital Input Card. A

30-conductor cable (28 gauge max. wire) is required to interconnect the card and the external device. The cable length should be kept as short as possible.

# SECTION IV PRINCIPLES OF OPERATION

### 4-1 INTRODUCTION

4-2 This section contains principles of operation for Digital Input Card, Model 69431A. Theory is presented on both a block diagram and a detailed circuit theory level.

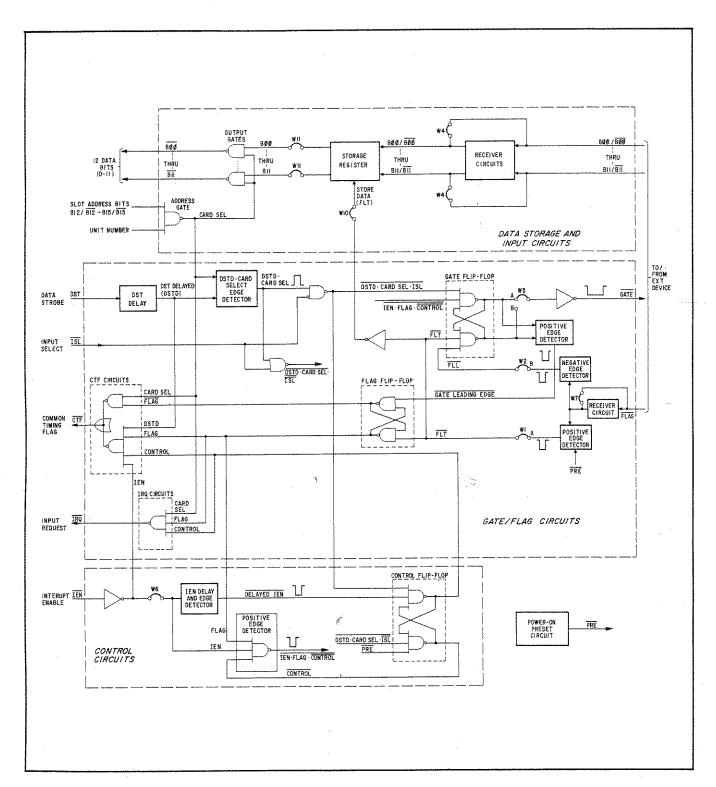

#### 4-3 BLOCK DIAGRAM THEORY

4-4 Figure 4-1 is a block diagram of the digital input card. The card consists of three main functional circuit groups: (1) data storage and input circuits which interface 12-bit external device data for input to the computer via the multiprogrammer main frame; (2) gate/flag circuits which exchange control timing signals with the multiprogrammer and external device to synchronize data transfers; and (3) a control circuit that stores the activation status of the digital input card. In addition to the three main functional circuit groups, the input card also includes a power turn-on preset circuit which initializes the digital input card functional circuits when multiprogrammer power is turned on.

### 4-5 DATA STORAGE AND INPUT CIRCUITS

4-6 The data storage and input circuits consist of an address gate, 12-bit receiver circuits, 12bit data storage circuits, and 12 output gates. When the input card slot is addressed in a multiprogrammer address word, the slot address bits all go to the HI state. If the unit containing the card was previously addressed in a multiprogrammer mode control word, U-- is also HI. When all address inputs are HI, the card select signal, applied to the data output gates and to the gate/flag circuits, is enabled. The card select signal couples the 12-bit input data from the output gates to the multiprogrammer main frame data bus. If the multiprogrammer is in the input select (ISL) mode, the 12 data bits appear at the return data lines (bits 0-11) from the multiprogrammer to the computer.

4-7 Data is entered into the input card storage circuits through the receiver circuits which convert, as necessary, user logic levels to the logic levels employed in the multiprogrammer. Depending upon user requirements, option jumpers and receiver circuit input bias networks are selected to interface the following logic sense and voltage level inputs: (1) negative-true TTL/DTL microcircuit-level input data (Option 069); (2) positive-true TTL/DTL microcircuit-level input data (Option 073);

and (3) open collector negative-true input data (Option 070). In addition, the receiver circuits can be modified to satisfy other interface requirements (such as relay contact closure input data). The jumper assignments required for the 069, 073, and 070 options are described completely in Section III.

4-8 With option jumper W10 installed, input data is stored in the data storage circuit when the device flag switches to the ready state (trailing edge). At the trailing edge of the device flag, the outputs of the receiver circuits are strobed into the data storage circuits. Notice that with jumper W10 removed, the flag trailing edge storage requirement is disabled so that the device input data appears at the output gates as received from the device.

#### 4-9 GATE/FLAG CIRCUITS

4-10 The digital input card gate/flag circuits consist of gate and flag flip-flop storage circuits as well as common timing flag (CTF) and input request (IRQ) identification circuits. The gate/flag circuits provide, in conjunction with the input card control circuits, data transfer synchronization among the programming source (via the multiprogrammer main frame, of course), digital input card, and external device. The functions performed by each of the gate/flag circuits are described below.

4-11 Gate Flip-Flop. The gate flip-flop synchronizes the start of data transfers between the computer and the external device. The gate flip-flop is set under program control to notify the device that the input card is ready to accept new data. The output of the gate flip-flop is applied to the external device through option jumper W5 which is used to provide either negative- or positive-true logic sense output. The output of the gate flip-flop is also applied to the flag flip-flop such that when the gate flip-flop is set, the flag flip-flop is reset to the busy state.

4-12 The gate flip-flop can be set (toggled) to begin data transfer operations in two ways, one of which requires that option jumper W6 be installed while the other does not depend on the W6 jumper. The second method of setting the gate flip-flop (the one not requiring the W6 jumper) is the usual way of controlling the flip-flop and requires that the card be selectively addressed. In this method, the gate flip-flop is set when the card is addressed in the ISL mode and in addition, a data strobe is

Figure 4-1. Digital Input Card, Model 69431A, Block Diagram

received. If jumper W6 is installed, however, the gate flip-flop can also be set and the input card activated by programming the IEN mode of operation assuming that the card is not busy (the flag flip-flop must be in the ready state) and the card has not been previously activated (the control flip-flop must be reset). Thus, if these conditions are met, the input card (and all input cards having W6 installed) will be activated and begin a data input transfer cycle when the IEN mode is programmed.

4-13 With the WI and W2 jumpers connected as shown, the gate flip-flop is reset by both the leading edge and the trailing edge of the device flag input. Some time after it receives the gate signal, the device should switch its flag input to the busy state (leading edge). Normally, at this transition, the gate flip-flop will be reset. However, under certain circumstances it may be possible to "hang up" the gate output of the input card. This might occur, for instance, if the input card gate flip-flop is toggled (set) a second time before the device signals that it is ready (trailing edge of device flag). Thus, if the gate flip-flop were reset only with the leading edge of the flag, and the gate flip-flop were set after the leading (busy) edge had been received, the gate line to the device might be locked up. As a precaution against this possibility, the trailing edge of the external device flag imput is also used to reset the gate flip-flop. Note that jumpers W1 and W2 can be connected to the same position (A or B) in which case the gate flipflop will be reset only with the trailing edge of the device flag input. See Section III for details.

4-14 Flag Flip-Flop. The input card flag flip-flop stores the data busy/ready status of the input card (and external device) for use in the common timing flag and input request circuits. The flag flip-flop is reset to the busy state when the gate flip-flop is set. At some time after the gate flip-flop is set, the external device should switch the flag input to the busy state. At a time determined by the specific external device, the device input data is made available to the input card. When data is ready, the device flag input should switch to the ready state (trailing edge). The trailing edge of the device flag causes the input card flag flip-flop to set to the ready state. The flag flip-flop remains in the ready state (set) until it is reset to busy again when the gate flip-flop is set.

4-15 The flag input passes through a receiver circuit that is similar to the data receiver circuits and which allows a variety of input flag logic sense and logic level input specifications to be accepted. Option jumpers W1 and W2 (in conjunction with W7, which allows optional logic level inputs to be used) provide for the reception of either negative—or positive—true logic sense flag inputs from the external device and allow the input card

gate to be reset with the ready and/or trailing edge of the device flag.

4-16 Common Timing Flag (CTF) Circuit. The input card's CTF output signal reflects the data readiness status of the input card and is used to signal the computer when data is available. The CTF circuit can be operated in two basic modes of operation. One mode, the dedicated input mode is used for simple data transfer sequences and requires that the input card be addressed before it can signal the computer (through the multiprogrammer main frame) that data is ready. The other mode, the interrupt search input mode, is used in more complex data transfer sequences (sequences in which several — up to 240 — input cards can be active at the same time) and does not require that the card be addressed before it can signal the computer that data is ready. Note that for either mode of operation, the multiprogrammer must be programmed to the timing mode (TME on) in order to allow the input card CTF output to control the multiprogrammer's flag output to the computer. If the multiprogrammer is not in the timing mode, it ignores the CTF line and generates an automatic (handshake) flag to the computer.

4-17 Dedicated Input Mode. In the dedicated input mode, the  $\overline{\text{CTF}}$  output of the input card follows the reset output of the flag flip-flop assuming that the input card address is enabled. When the flag flip-flop is reset to the busy state, then the  $\overline{\text{CTF}}$  output goes LO to indicate that the input card is busy.  $\overline{\text{CTF}}$  stays LO until the flag flip-flop switches to the ready state at which time  $\overline{\text{CTF}}$  goes HI to notify the computer that data is available. This data transfer sequence is repeated as long as the input card is addressed.

4-18 Interrupt Search Input Mode. In the interrupt search input mode, the interrupt enable mode (IEN) is on (as well as TME in the multiprogrammer) and the CTF line is controlled by both the input card flag flip-flop (set output) and the data strobe (DST) input to the card. When the flag flip-flop is set to the ready state with IEN and the delayed DST both on, the CTF output goes LO. The LO state of CTF should cause the computer to switch the DST input to the LO state. When DST goes LO, the CTF output goes HI and the computer is notified that data is available. Notice that the computer program entirely controls the operation of the input card gate/ flag and CTF circuits and must, in addition, interpret the subsequent data ready/busy reaction of the input card as reflected in the CTF output.

4-19 Input Request (IRQ) Identification Circuit. The IRQ circuits aid the computer in determing the data ready/busy status of the input card (especially in the interrupt search mode which involves many input cards any one of which can signal the

computer that data is ready via the CTF line). The IRQ output is enabled (LO) when the input card is addressed, the flag flip-flop is set to ready, and the card is activated (control flip-flop is set). When these conditions have been met, the IRQ output goes LO and is combined with the IRQ output of all other input cards (only the addressed card controls the common IRO line, however) in the multiprogrammer main frame. Further, assuming the ISL mode is on, the multiprogrammer combines the  $\overline{\mathbb{RQ}}$ signal with the bit 15 return data line that it sends to the computer. Thus, bit 15 of the data returned to the computer when an input card is addressed in the ISL mode reflects the data ready state of the addressed input card. In the interrupt search mode, then, the computer can interrogate (address) each of the active cards in a software-controlled priority and determine which one is ready with data by examining the state of bit 15 returned with the input card's data bits.

#### 4-20 CONTROL CIRCUITS

4-21 The control circuits include a control flipflop that stores the activation status of the input card. In addition, the control circuits process the IEN input when the W6 jumper is installed. Like the gate flip-flop, the control flip-flop is set when the input card is activated (the card is addressed and strobed in the ISL mode or, if jumper W6 is installed, when IEN is programmed). The control flipflop remains set until the card is deactivated (the card is addressed and strobed and the ISL mode is off). When set, the control flip-flop enables (along with IEN, the flag flip-flop, and DST) the CTF line during the interrupt search mode of operation. Similarly, the control flip-flop enables (along with the card address and flag flip-flop) the IRO output of the input card.

4-22 If the W6 jumper is installed, the control circuits receive and process the IEN input. When IEN is programmed (IEN goes LO), the processing circuits set the control flip-flop after a delay of approximately 0.5µsec. The delay is utilized to prevent the input card's gate flip-flop from being set when IEN is programmed on and the control flip-flop is already set (activated). Further, the gate flip-flop is not set when IEN is programmed if the flag flip-flop is in the busy state (reset). Under these conditions, the card must have been previously activated and then subsequently deactivated with the gate/flag circuits still timing out; therefore, the gate flip-flop is prevented from be-. ing re-toggled when IEN is programmed on. Of course, if the card is in the data ready state (flag flip-flop is set) and the control flip-flop is off, the gate flip-flop is set to initiate a data transfer cycle. In addition, the control flip-flop is set after the delay period. Thus, with the W6 jumper installed on several input cards,

the program can activate the entire group at one time. Note, however, since it is possible to reactivate a card (set the control flip-flop) that had been previously deactivated, the IEN jumper should be used with discretion in controlling the activation of input cards.

#### 4-23 POWER-ON PRESET

4-24 When multiprogrammer power is turned on, the preset circuit initializes the input card. The preset circuit generates a pulse that is used to generate the device flag leading and trailing edge pulses. The simulated device flag pulses, of course, reset the gate flip-flop and set the flag flip-flop to the ready state. In addition, the flag trailing edge pulse strobes the device data lines into the input card data storage circuits. The preset pulse is also applied directly to the control flip-flop where it resets the flip-flop and, consequently, deactivates the input card upon power turn-on.

### 4-25 GATE/FLAG/CONTROL CIRCUIT TIMING

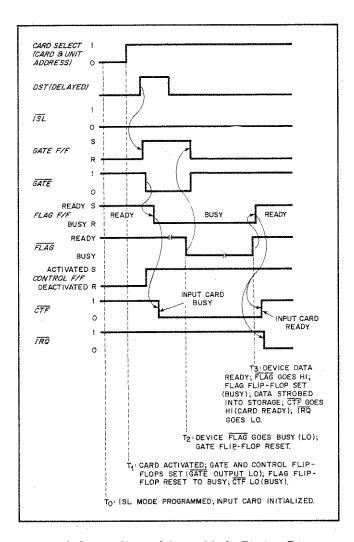

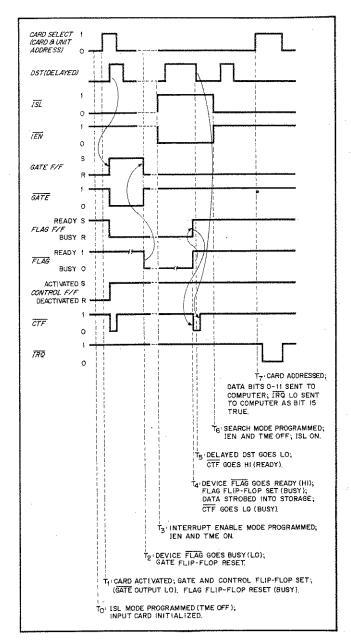

4-26 Timing diagrams of the signals generated by the gate/flag and control circuits in the two basic modes of operation, the dedicated input and interrupt search input modes, are given in Figures 4-2 and 4-3, respectively. The timing diagrams assume that negative-true gate and flag signals are utilized and that the gate signal is to be reset at the leading edge of the flag (this is the 069 option). Further, it is assumed that the W10 jumper is still installed (which means that the device flag trailing edge is required for input data storage).

4-27 <u>Dedicated Input Mode</u>. The timing relationships of signals exchanged among the multiprogrammer, input card, and external device in the dedicated input mode are depicted in Figure 4-2 and described below:

$T_0$  — At  $T_0$ , the multiprogrammer has been programmed into the ISL mode. The input card was previously initialized (either as a result of the last data transfer cycle or if power were turned on) so that the gate and control flip-flops are reset and the flag flip-flop is set (ready).

$T_1$ —The input card is now activated with the combination of the card (and unit) address and the data strobe. The gate and control flip-flops are set with the LO state of the  $\overline{GAT}$  output to the external device signaling the device that the input card can accept data. When set, the gate flip-flop also resets the flag flip-flop to the busy state which causes the  $\overline{CTF}$  output to switch LO (card busy). Input data is available to the computer as long as card is addressed.

$T_2$  — In response to the  $\overline{GAT}$  signal, the device  $\overline{FLG}$  input switches busy (LO). The leading edge of  $\overline{FLG}$  resets the gate flip-flop which switches the  $\overline{GAT}$  output HI.

Figure 4-2. Dedicated Input Mode Timing Diagram

T3 - Device times out and is ready with data. The FLG input goes HI; trailing edge of FLG sets flag flip-flop and strobes data into storage. When set (ready) flag flip-flop switches CTF output to HI (card ready). IRQ also goes LO. Notice that the input card's CTF output is used to signal that the card is ready with data for the computer. The card address must be enabled, then, for this output to be generated and, in addition, the multiprogrammer must be in the timing mode (TME on) to allow the CTF line to control the multiprogrammer flag line to the computer. If the multiprogrammer is not in the timing mode (TME is off), the multiprogrammer returns an automatic flag (handshake flag) and ignores the input card CTF flag. Thus, computer software will be required to determine when the card has data ready which it can do by examining bit 15 of the data returned by the card. Bit 15, it will be recalled, contains the data readiness status of the input card as indicated by the IRQ output.

4-28 <u>Interrupt Search Input Mode</u>. The timing relationships of signals exchanged among the

Figure 4-3. Interrupt Search Input Mode Timing Diagram

multiprogrammer, input card, and external device in the interrupt search input mode are depicted in Figure 4-3 and described below:

T0-T2—The first steps of the interrupt search input mode are similar to the dedicated input mode. The input card is activated in the ISL mode; the external device should respond with a busy  $\overline{FLG}$  (LO) after the input card  $\overline{GAT}$  signal goes LO. Notice that the input card address is not maintained and that the multiprogrammer should be in the handshake mode (TME off) so that the CTF generated during input card activation will be ignored by the multiprogrammer (and computer). After the input card is activated, in addition, the computer can activate all

other desired input cards. It is assumed that during the activation of the other input cards, the external device responds to the  $\overline{GAT}$  signal by switching the  $\overline{FLG}$  input busy (LO). The device busy  $\underline{fLag}$  could, of course, occur at any time after the  $\overline{GAT}$  signal goes LO.

T3-After activating all desired input cards, the multiprogrammer is programmed to the interrupt enable mode in which IEN and TME are on and ISL can be either on or off (it is assumed that the program turns ISL off).

$T_4$  - The system now waits for an external device to time out and signal that data is ready. When ready, the device switches its FLG input HI which sets the input card flag flip-flop to the ready state. The setting of the flag flip-flop causes the input card  $\overline{\text{CTF}}$  signal to go LO (busy). The trailing edge of the  $\overline{\text{FLG}}$  input also strobes the device data into storage. Notice that since the ready status of the external device as well as the device input data is stored on the input card, the interrupt enable mode (T3) could actually follow the device ready FLG transition and data input (in that case, when IEN is programmed on, CTF will go LO). Notice further, that even if the W6 jumper is still installed, IEN will not affect the input card gate flip-flop because the card's control flip-flop was set as a result of selective card activation.

T5-When  $\overline{\text{CTF}}$  switches LO, and assuming the multiprogrammer is in the timing mode (TME is on), the multiprogrammer flag to the computer causes the computer interface card to switch the DST input LO (the DST input is derived from the computer gate input to the multiprogrammer). When DST goes LO, the input card  $\overline{\text{CTF}}$  output switches HI (ready) which is the signal to the computer that data is available from an input card.

$T_6$  - Since any one of the activated input cards could have signalled that data is ready, the computer enters the search mode during which it, will interrogate (address) each of the cards (in a software-determined priority) to determine which one is ready. In the search mode, the interrupt enable mode is turned off (to prevent data ready interrupts from other input cards) and the ISL mode is turned on. The timing mode is usually turned off (TME off) also to allow the fastest method (handshake) of communicating with the input cards.

T7-The computer now searches for the ready card. The card is addressed (without a data strobe in order to prevent reactivation of a busy card) and its data is returned to the computer on the multiprogrammer's return data lines. The computer must examine (by software) bit 15 (which includes the status of the  $\overline{\rm IRQ}$  signal) to determine if the card data it received is valid (ready) data. Note that when a ready card is addressed, its  $\overline{\rm IRQ}$  output is LO so that the bit 15 return line will be true.

4-29 After identifying the ready input card, the program has several options. It can deactivate the

the card (address the card with a data strobe after turning ISL off); it can reactivate it; it can (after deactivating or reactivating the previously ready card) turn the interrupt enable mode back on and wait for the next input card to signal ready, etc. In any case, the program should at least take action with regard to input cards from which it accepts valid data. The card should be either reactivated or deactivated. If no more data is expected from the card, it should be deactivated in order to prevent the card from generating its  $\overline{\text{CTF}}$  output when the interrupt mode is turned on again for other active cards. Deactivating the input card resets its control flip-flop which disables the  $\overline{\text{CTF}}$  output during the interrupt enable mode.

## 4-30 DETAILED CIRCUIT ANALYSIS (See Figure 7-1)

### 4-31 DATA STORAGE AND INPUT CIRCUITS

4-32 Receiver Circuit. The configuration of the receiver circuit depends on the input card option in use. For microcircuit logic level options 069 and 073, only a lkn pull-up resistor is provided in the input network and data inputs are jumpered directly to the storage register flip-flops. Open collector option 070, however, requires an input bias network and receiver gate as shown in Figure 7-1 in which case the jumpers are configured as listed on the schematic. The operation of the 070 receiver circuit is described below.

4-33 The Option 070 receiver circuit is comprised of a hybrid integrated circuit inverting gate (G1-G12) and an associated input bias network. The three resistors of the input bias network are selected so that a high (positive voltage) input level drives the inverter into full conduction while a low input level cuts the inverter off. Thus, the open collector input logic levels are converted to microcircuit logic levels with the output of the receiver circuit applied to the data storage register.

4-34 <u>Data Storage</u>. The 12-bit data storage register is comprised of three. 4-bit storage flip-flops, Z1 through Z3. Each flip-flop is a D-type, positive-edge triggered circuit. If storage disable jumper W10 is installed, the logical state at the D-input of a flip-flop is transferred to the Q output terminal when the clock terminal (CLK) is strobed by a positive-going device flag trailing-edge pulse. The  $\overline{Q}$  output always assumes the state opposite the Q output. If the W10 jumper is removed, the CLK input is held positive and the D-input (data) controls the state of the flip-flop directly. Thus, with W10 removed, data appears at the output of the flip-flops as applied from the receiver circuits.

4-35 The Q or  $\overline{Q}$  outputs of the storage flip-flops are selected by jumpers W11 such that, depending

upon the logic sense of the input data and the installation of the W4 receiver circuit jumpers, the binary logic value of input to the data output gates is always the same as the binary logic value of the original data input to the receiver circuits. For example, if the 069 (negative-true microcircuit logic level) option is in use, a binary 1 (LO) is jumpered through W4 to reset the associated storage flip-flop. The output, however, is taken from the reset side and is, thus, a logic one (converted to positive-true). Note, further, that the output gates invert the data bit outputs of flip-flops so that the input to the multiprogrammer is always negative-true data.

4-36 Address and Output Gates. When the slot and unit in which the input card is inserted are addressed, the four address bits and U-- go HI. Data bits BØØ through Bll are transferred through the output gates to the multiprogrammer data bus as data bits  $\overline{B00}$  through  $\overline{B11}$ . If the multiprogrammer has been programmed into the input select (ISL) mode, the data bits are sent to the computer over the multiprogrammer return data lines (bits B00 -B11). The card select output of the address gate (G14) is also applied to the gate/flag circuits where it is used for the following functions: (1) enables the CTF output during dedicated input mode of operation; (2) enables the IRQ output when the card is activated and ready; and (3) used, in combination with the data strobe and ISL inputs, to activate or deactivate the input card.

### 4-37 GATE/FLAG CONTROL CIRCUITS

4-38 Detailed circuit operation of the gate/flag and control circuits is presented for the following phases of operation:

- a. Selective card activation

- b. Start-of-gate and CTF

- c. Start-of-flag

- d. End-of-flag and CTF/IRQ

- e. Card activation with IEN

- f. Card deactivation.

4-39 Selective Card Activation. The input card gate/flag and control circuits are selectively activated when the card is addressed (the card select output of G14 is enabled) after the ISL mode has been programmed and the data strobe (DST) is received. The HI DST signal is first applied to inverter G15 the output of which is  $\overline{\text{DST}}$ . The  $\overline{\text{DST}}$  signal next passes through a delay circuit comprised of resistor R6 and capacitor C12. Before DST goes LO; C12 is charged to approximately +3.5V, holding the input to inverter G16 at the logic one level. The inverted (LO) output of G16 holds NAND gate G17 disabled. When DST goes LO, C12 starts to discharge towards 0 volts through R6. After approximately 4μsec, C12 discharges to the zero logic level (approximately 0.8 volts). The delayed DST (DSTD)

signal is inverted to logic one through G16 to enable NAND gate G17. When the  $\overline{\rm DST}$  output of C15 goes  $\overline{\rm HI}$ , capacitor C12 charges rapidly to 3.5 volts through diode CR2 in preparation for the next DST input. Note that DST is delayed in order to prevent the input card from generating an erroneous  $\overline{\rm CTF}$  signal when the IEN mode is programmed off as part of the interrupt search mode of operation (see Paragraph 4-52).

4-40 After the 4µsec delay, the logic one DSTD output of inverter G16 is combined with the enabled card select input in NAND gate G17. The output on NAND gate G17,  $\overline{\text{CARD SELECT} \cdot \text{DSTD}}$ , is applied to a negative edge detector circuit (G18-G20, R8, and C7) which generates a short-duration negative pulse beginning at the leading edge of delayed DST. The negative pulse is used to control the setting of the gate and control flip-flops (it is also used to reset the control flip-flop during card deactivation, see Paragraph 4-55). The operation of the negative edge detector is described in the following paragraphs.

4-41 The negative edge detector circuit makes use of the discharge time of capacitor C7 to generate a negative pulse to set the gate and control flip-flops (card activation) and reset the control flip-flop (card deactivation). At the time CARD SELECT • DSTD initially goes LO, capacitor C7 begins to discharge, but, since it cannot discharge instantaneously, it temporarily holds one input to G19 HI. G18 inverts CARD SELECT • DSTD and holds the second input to G19 HI. The resulting LO pulse output of G19 is applied to inverter G20 which produces a shortduration positive pulse for combination with the input select (ISL) input. Note that the pulse width is determined by the discharge time of capacitor C7. When C7 has discharged to the LO logic level, gate G19 is inhibited and its output goes HI.

4-42 During the selective card activation process, the multiprogrammer is in the input mode and input  $\overline{\rm ISL}$  is LO. The CARD SELECT DSTD pulse is combined with ISL to set the gate and control flip-flops. The positive pulse is applied to NAND gate G21 which also receives the HI ISL output of inverter G22. The pulse is coupled through the NAND gate, then, and the resultant negative pulse sets the gate flip-flop (cross-coupled NAND gates Z13) and the control flip-flop (cross-coupled NAND gates Z12). The input card is now activated with the gate and control flip-flops in the set state.

4-43 Start-of-gate and CTF. The output of the gate flip-flop is inverted by driver Q3 and applied to output pin 13 for application to the external device. Jumper W5 allows either the set side of the gate flip-flop to be applied to Q3 or the reset side depending upon the logic sense requirements of the user's device. The transition (gate flip-flop set) of

the GATE/ $\overline{\text{GATE}}$  signal should initiate the timing cycle of the external device which should also respond with a  $\overline{\text{FLAG}}$  busy input to the card at some time after the  $\overline{\text{GATE}}$  transition.

4-44 The set output of the gate flip-flop is also applied to a positive edge detector which generates a short-duration negative pulse that is used to reset the flag flip-flop when the gate flip-flop is set. The positive edge detector is comprised of NAND gate G22, resistor R7, and capacitor C8 and operates like the negative edge detector previously described in that the positive edge detector also makes use of the discharge time of a capacitor (C8) to generate a negative pulse to reset the flag flipflop. At the time that the gate flip-flop is set, the reset side goes LO and capacitor C8 begins to dischange. The capacitor cannot discharge instantaneoulsy, however, so that it temporarily holds one input to NAND gate G22 HI. The second input to the gate is instantaneously HI when the gate flipflop is set. The resulting LO pulse output of G22 is applied to the flag flip-flop and resets the flipflop to the busy state.

4-45 As described above, the activation of the input card results in the gate and control flip-flops being set and the flag flip-flop reset to the busy state. The flag flip-flop will remain in the busy state until the external device FLAG input switches busy (leading edge) and then back to ready (trailing edge). Note, however, that if the input card is in the dedicated input mode of operation, i.e. the card's address is enabled after the card is activated, the inputs to NAND gate G23 are HI. The LO output of the gate is inverted by NOR gate G24 and again by driver Q4 and applied to output pin 7 for application as the LO CTF signal to the multiprogrammer. If the multiprogrammer is also in the TME mode, the LO  $\overline{ ext{CTF}}$  signal will control the multiprogrammer flag output to the computer such that the leading edge of the CTF signal notifies the computer that the input card is busy (flag flip-flop reset) processing a data transfer cycle with its external device. In this mode, the card address should be maintained until the device signals ready in order to keep the  $\overline{\text{CTF}}$  line LO.

4-46 If the input card is not in the dedicated input mode, the resetting of the flag flip-flop during card acitvation will also set the  $\overline{\text{CTF}}$  line LO since the card address will be enabled for a period after the flag is reset. However, the card address is not maintained during the interrupt search mode so that the  $\overline{\text{CTF}}$  output will switch HI after the address is removed. Thus, when a card is activated as part of the interrupt search input mode, the toggling of the  $\overline{\text{CTF}}$  output should be ignored by the computer (if the multiprogrammer is not in the timing mode, for instance, the  $\overline{\text{CTF}}$  signal will be ignored in the multiprogrammer and will not control the

multiprogrammer flag to the computer).

4-47 Start-of-flag. When the external device responds to the input card GATE signal, it generates the start-of-flag input by switching the FLAG input to the card to the busy state. The FLAG input passes through a receiver circuit that is functionally identical to the data bit receiver circuits (the FLAG receiver is comprised, however, of discrete components while the data bit receivers employ hybrid integrated circuits). The FLAG receiver includes a jumper, W7, that allows either microcircuit or open collector logic level FLAG inputs to be used.

4-48 After interfacing by the receiver circuit, the  $\overline{\rm FLAG}$  signal in inverted by G25 and applied to a lµsec delay circuit comprised of resistors R1 and R2 and capacitor C16. The lµsec delay of the  $\overline{\rm FLAG}$  signal reduces the susceptibility of the input circuits to transients. Resistor R11, connected between the output of G26 and G27, provides hysteresis to prevent oscillation with the increased rise time of Z11.

4-49 The combination of gates G26, G27, and G28 and resistor R3 and capacitor C10 comprise a positive edge detector while G26, G27, G29, and resistor R4 and capacitor C11 comprise a negative edge detector. The operation of the detectors is similar to the edge detectors previously described. The W1 and W2 jumper connections are selected in conjunction with the W7 jumper and the logic sense of the FLAG input such that the short-duration negative FLL and FLT pulses at the output of the positive and negative edge detectors are selected at the leading and/or trailing edges of the FLAG input depending on whether the gate flip-flop is to be reset at the leading or trailing edge of the flag input. For example, if the negative-true TTL/DTL option (069) is desired and the gate is to reset at the flag leading edge, W1 is connected to A and W2 is connected to B (W7 is also installed). Thus, when the FLAG input switches busy (LO), the positive edge detector produces a negative pulse (at the output of G28) that is coupled through W2 as the  $\overline{\text{FLL}}$  signal and applied to the gate flip-flop to reset it in preparation for the next input card activation operation. See Section III for complete details on the W1 and W2 (as well as W7) jumper connections required to establish the various  $\overline{\text{FLAG}}$  polarity and gate reset configurations.

4-50 End-of-flag and CTF/IRQ. When the external timing circuit times out, the FLAG input to the input card switches to the ready state (trailing edge). The positive- or negative-edge detector will produce a negative pulse at this time depending upon the logic sense input and corresponding jumper connections as described above. For the 069 option, the negative edge detector produces a negative pulse (at the output of G29) that is coupled through

W1 as the  $\overline{\text{FLT}}$  signal. The  $\overline{\text{FLT}}$  pulse is applied to the flag flip-flop to set it to the data ready state. In addition,  $\overline{\text{FLT}}$  is inverted by driver Q7 which, if storage disable jumper W10 is installed, couples the positive FLT pulse to the 12-bit storage register to strobe the input data into storage. The card is now in the data ready state with the flag flip-flop set and the data stored in the storage register. When the flag flip-flop is set, it controls the  $\overline{\text{CTF}}$  and  $\overline{\text{IRQ}}$  outputs of the card as determined by the mode of operation, dedicated input mode or interrupt search input mode, currently in effect.

4-51 If the dedicated input mode has been established, the card address is enabled when the flag flip-flop is set and, therefore, the  $\overline{\text{CTF}}$  output of driver Q4 goes HI (it went LO when the flag flip-flop was reset). Assuming, further, that the timing mode is in effect (TME is on), the HI transition of the  $\overline{\text{CTF}}$  output notifies the computer that the card has data ready for the computer. Notice, too, that the  $\overline{\text{IRQ}}$  output of driver Q1 is also LO at this time and can be used, if necessary, by the computer to determine if the card's data is valid (ready).

4-52 If the interrupt search mode is in progress, the card address is not enabled. Instead, the IEN and delayed DST inputs to NAND gate G30 are enabled as well as the control flip-flop input. Thus, when the flag flip-flop sets, the  $\overline{\text{CTF}}$  output of Q4 goes LO. This LO transition of  $\overline{ ext{CTF}}$  (assuming TME is on) should cause the computer to disable the multiprogrammer's DST input (which is derived from the computer gate) at which time NAND gate G30 is disabled and the  $\overline{\text{CTF}}$  output switches back to HI. The HI transition of  $\overline{\text{CTF}}$  notifies the computer that the input card has data ready. When the computer, in its search mode (IEN off and ISL on) addresses the card, the  $\overline{\text{IRQ}}$  output of Q1 is returned in bit 15 to the computer (which also, of course, receives the card's 12 data bits at the same time). Bit 15, then, is examined by the computer program to determine the validity of the data it receives from the input card. Notice that before it enters the search routine, the computer programs IEN off to prevent other input cards from generating CTF interrupts during the search process. Thus, DST is delayed on the input card to prevent this same card from again generating the CTF output which would occur since DST is used to reset IEN in the multiprogrammer main frame.

4-53 <u>Card Activation with IEN</u>. Jumper W6 allows the input card, along with all other input cards on which the jumper is also installed, to be activated (that is, the gate and control flip-flop set and the flag flip-flop reset) when the IEN mode is programmed in the multiprogrammer. If W6 is not installed, the card must be selectively activated and cannot be activated with IEN. The IEN input from inverter G31 (also used in the CTF circuits as previously